# Normally-off Transistor Topologies in Gallium Nitride Technology

Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorlegt von

## Gerrit Lükens, M.Sc.

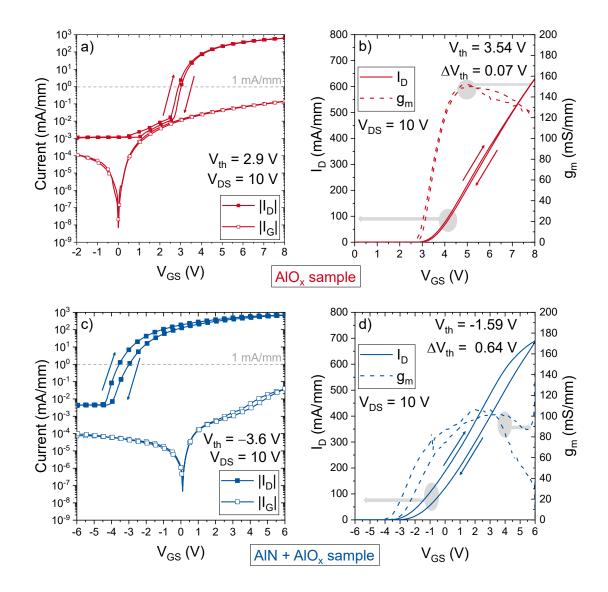

aus Lübbecke

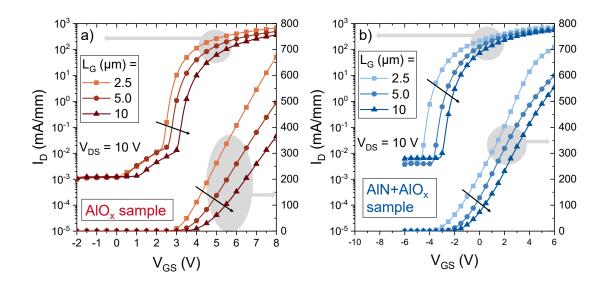

Berichter: Universitätsprofessor Dr.-Ing. Andrei Vescan Universitätsprofessor Dr.-Ing. Max Christian Lemme

Tag der mündlichen Prüfung: 13.02.2020

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

# Contents

| 1. | Intro                                        | duction                                                                                  | 1  |  |  |  |  |

|----|----------------------------------------------|------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2. | Fundamentals of Group III Nitride Technology |                                                                                          |    |  |  |  |  |

|    | 2.1.                                         | Crystal Structure                                                                        | 5  |  |  |  |  |

|    | 2.2.                                         | Bandgap and Polarization                                                                 | 7  |  |  |  |  |

|    | 2.3.                                         | Heterostructures and the Two-Dimensional Electron Gas                                    | 9  |  |  |  |  |

|    | 2.4.                                         | Electron Mobility in the 2DEG                                                            | 12 |  |  |  |  |

|    | 2.5.                                         | Heterostructure Field-Effect Transistor                                                  |    |  |  |  |  |

|    | 2.6.                                         | Dielectrics in an HFET                                                                   | 18 |  |  |  |  |

|    |                                              | 2.6.1. Electrostatics of a MISHFET                                                       | 18 |  |  |  |  |

|    |                                              | 2.6.2. Surface Passivation of the Access Regions                                         | 20 |  |  |  |  |

|    |                                              | 2.6.3. Gate Insulation of the intrinsic HFET                                             | 21 |  |  |  |  |

| 3. | Electrical Characterization Methods          |                                                                                          |    |  |  |  |  |

|    | 3.1.                                         | Capacitance-Voltage (C-V)                                                                | 25 |  |  |  |  |

|    | 3.2.                                         | Current-Voltage (I-V)                                                                    | 28 |  |  |  |  |

|    | 3.3.                                         | Pulsed-I-V                                                                               | 30 |  |  |  |  |

| 4. | Thre                                         | shold Voltage Engineering and Stability of MISHFET                                       | 33 |  |  |  |  |

|    | 4.1.                                         | Plasma-Enhanced Atomic Layer Deposition                                                  | 33 |  |  |  |  |

|    | 4.2.                                         | Interface Trap States                                                                    | 35 |  |  |  |  |

|    | 4.3.                                         | Metal-Insulator-Semiconductor HFET                                                       | 38 |  |  |  |  |

|    | 4.4.                                         | Post-Depositon Anneal                                                                    | 41 |  |  |  |  |

|    | 4.5.                                         | Pre-deposition Plasma Oxidation                                                          | 45 |  |  |  |  |

|    | 4.6.                                         | Limitations of positive $V_{th}$ shift through dielectrics $\ldots \ldots \ldots \ldots$ | 52 |  |  |  |  |

|    | 4.7.                                         | Flash-like MISHFET Memory Effect                                                         | 56 |  |  |  |  |

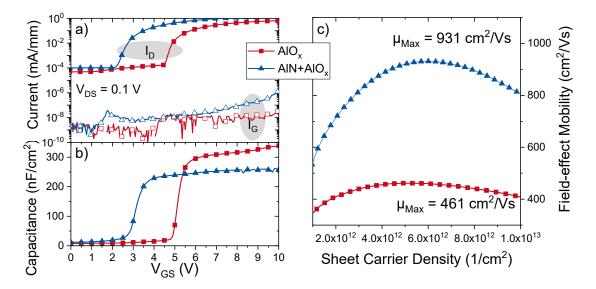

| 5. | Mobility Enhancement in MIS-hybrid HFET      |                                                                                          |    |  |  |  |  |

|    | 5.1.                                         | Metal-insulator-semiconductor-hybrid HFET                                                | 63 |  |  |  |  |

|    | 5.2. Mobility Enhancement by an Amorphous AlN Spike |                |                                                             |            |  |  |  |  |  |

|----|-----------------------------------------------------|----------------|-------------------------------------------------------------|------------|--|--|--|--|--|

|    |                                                     | 5.2.1.         | PEALD of Amorphous Aluminum Nitride                         | 66         |  |  |  |  |  |

|    |                                                     | 5.2.2.         | Comparison of MIS-hybrid HFET with and without amorphous    |            |  |  |  |  |  |

|    |                                                     |                | AlN spike                                                   | 68         |  |  |  |  |  |

|    |                                                     | 5.2.3.         | Electrical characteristics of MIS-hybrid HFET with standard |            |  |  |  |  |  |

|    |                                                     |                | geometry                                                    | 70         |  |  |  |  |  |

| 6. | Processing of p-GaN-gated AIGaN/GaN HFET            |                |                                                             |            |  |  |  |  |  |

|    | 6.1.                                                | p-GaN          | -gated HFET                                                 | 75         |  |  |  |  |  |

|    | 6.2.                                                | Selecti        | ve Etching of p-GaN                                         | 83         |  |  |  |  |  |

|    | 6.3.                                                | Self-al        | igned Gate Patterning                                       | 84         |  |  |  |  |  |

|    | 6.4.                                                | Compl          | lete Manufacturing Process                                  | 87         |  |  |  |  |  |

|    | 6.5.                                                | High-V         | Voltage Device                                              | 89         |  |  |  |  |  |

|    |                                                     | 6.5.1.         | Elevated-Temperature Operation                              | 94         |  |  |  |  |  |

|    | 6.6.                                                | Increas        | sed-Threshold-Voltage Device                                | 99         |  |  |  |  |  |

|    | 6.7.                                                | Advan          | ced Concepts                                                | 101        |  |  |  |  |  |

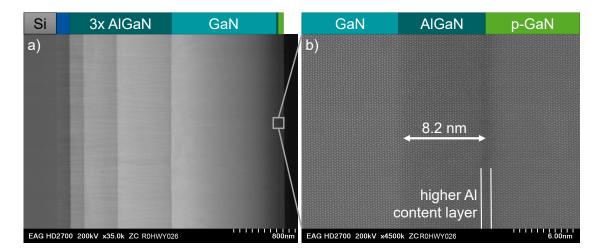

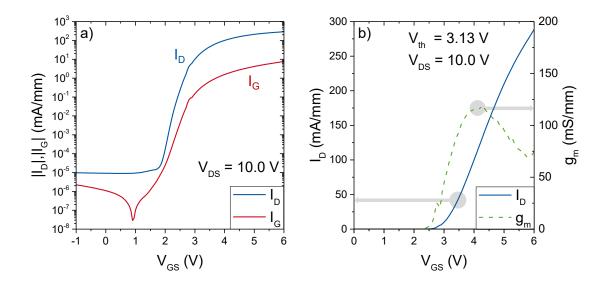

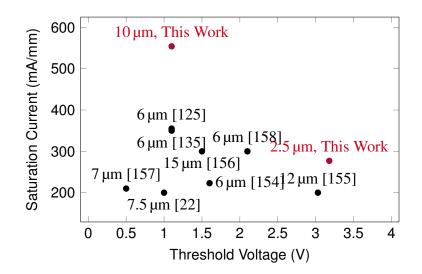

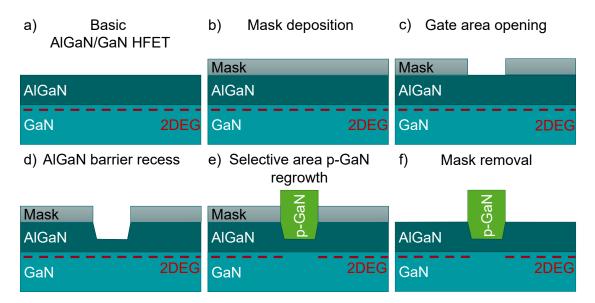

|    |                                                     | 6.7.1.         | Selective-Area Regrowth p-GaN-gated HFET                    | 102        |  |  |  |  |  |

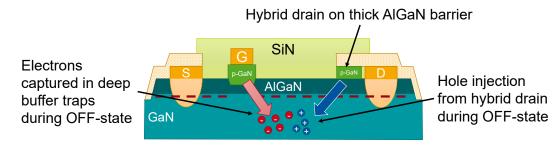

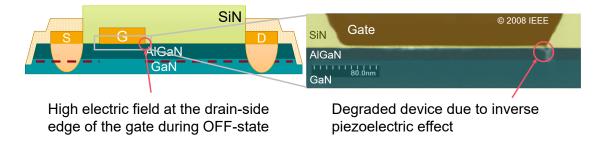

|    |                                                     | 6.7.2.         | p-GaN Hybrid Drain                                          | 103        |  |  |  |  |  |

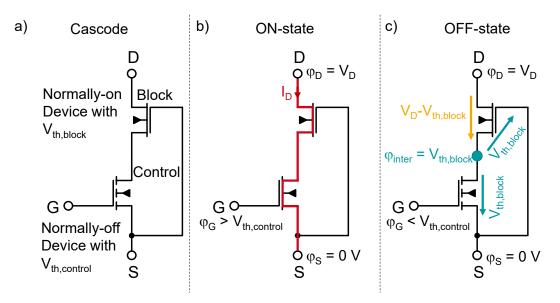

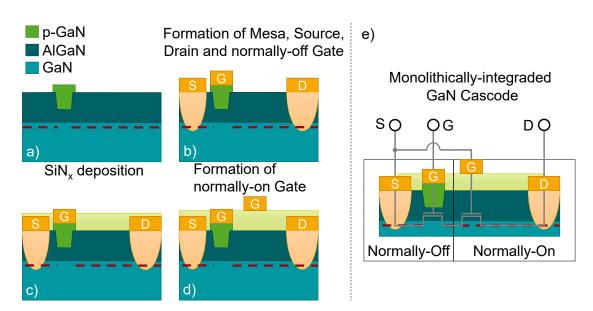

|    |                                                     | 6.7.3.         | Monolithically-integrated GaN Cascode                       | 104        |  |  |  |  |  |

| 7. | Con                                                 | npariso        | on of MISHFET, MIS-hybrid HFET and p-GaN-gated HFET         | 109        |  |  |  |  |  |

| 8. | Con                                                 | clusio         | n and Outlook                                               | 115        |  |  |  |  |  |

| A. | Арр                                                 | endix          |                                                             | 119        |  |  |  |  |  |

|    | A.1.                                                | Param          | eters for Calculations                                      | 119        |  |  |  |  |  |

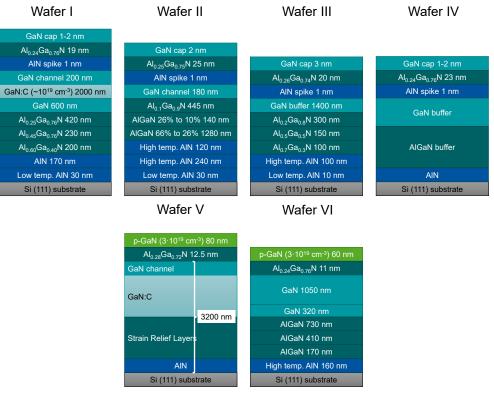

|    | A.2.                                                | Wafer          | List                                                        | 120        |  |  |  |  |  |

|    | A.3.                                                | Overvi         | iew TCAD-Simulations p-GaN-gated-HFET                       | 120        |  |  |  |  |  |

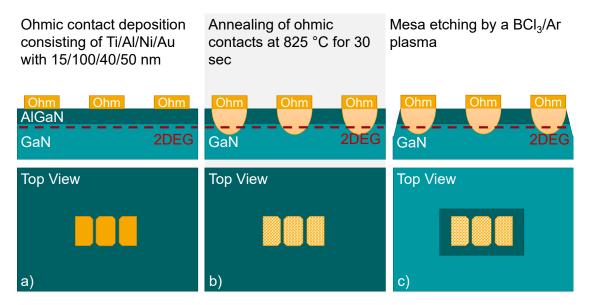

|    | A.4.                                                | Basic          | HFET Processing                                             | 121        |  |  |  |  |  |

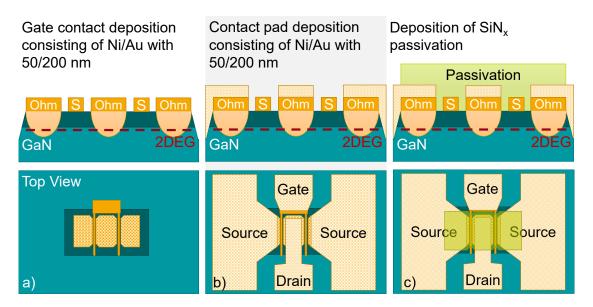

|    |                                                     |                | e Geometries                                                |            |  |  |  |  |  |

| _  | References 1                                        |                |                                                             |            |  |  |  |  |  |

| Re | eferei                                              | nces           |                                                             | 144        |  |  |  |  |  |

|    |                                                     | nces<br>Figure | s                                                           | 144<br>155 |  |  |  |  |  |

| Li | st of                                               |                |                                                             |            |  |  |  |  |  |

## 1. Introduction

Digitalization is rapidly evolving with an ever-growing pace. Information technology is nowadays omnipresent in our everyday life starting from the smartphones in our pockets, over Internet-of-Things (IoT) devices [1] in our homes, to smart grids on a European level [2]. While one part of the emerging products drive an increasing demand for electrical energy, e.g. electric vehicles, CPU-intensive concepts like blockchain [3] or industry 4.0 solutions [4], another part is focused on clean power generation, distribution, storage and efficient conversion to fulfill the grand quest for green and sustainable energy.

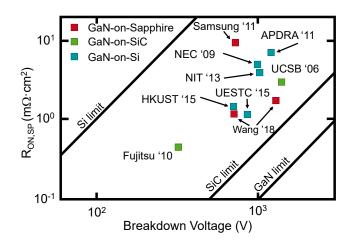

III/V compound semiconductors offer a high flexibility in terms of material properties [5] and are perfectly suited for these demands. By mixing different compounds, a wide range of bandgaps, electron mobilities and saturation velocities can be achieved. Particularly the group III nitride semiconductors (GaN, InN, AlN) are a key enabler for compact and efficient high-power applications.

Driven by the GaN LED market [6, 7], constant progress in deposition and substrate technology was made and the maturity of the whole GaN process chain increased significantly in the past decades. During this development, the invention of lateral Al-GaN/GaN heterostructure field-effect transistors (HFET) [8] was then seen as the next step in the radar and wireless communications sector [9, 10]. Today, GaN RF power amplifiers are commercially available and are also expected to be a backbone of the new 5G infrastructure [11]. These devices rely on the strong internal polarization of the nitrides to create a two-dimensional electron gas (2DEG) with high carrier densities and mobilities, which enable RF devices with high RF power densities.

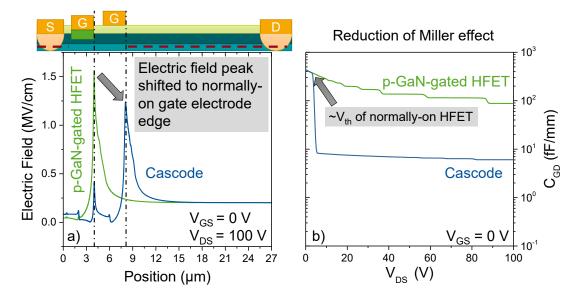

For high-voltage power amplifiers however, which are needed in e.g. DC/DC converters, GaN technology has a major drawback. Lateral heterostructure devices are inherently normally-on, i.e. they conduct current when no gate voltage is applied. This raises safety concerns because in case of a gate driver malfunctioning, the GaN transistor is not automatically switched off and uncontrolled current flow can damage the entire system. Furthermore, normally-on transistors make circuit designs more complex because a negative-voltage supply is required. Thus, a lot of research was focused on creating normally-off devices in recent years. Different topologies have been established: a cascode configuration of a silicon normally-off MOSFET and a normally-on GaN HFET [12, 13], HFET with fluorine implantation under the gate [14, 15], gaterecessed (metal-insulator-semiconductor, MIS)-HFET with partial [16–18] or complete AlGaN barrier removal [19, 20], and the p-GaN-gated HFET [21–23].

All of these concepts are aimed at stable positive threshold voltages  $V_{th}$ , while retaining the benefits of the AlGaN/GaN heterostructure, with their individual pros and cons: The advantage of the cascode is the avoidance of normally-off GaN HFET by controlling the device through a normally-off silicon MOSFET, while the GaN transistor blocks high voltages in OFF-state. The drawback is an overall limitation by using silicon regarding e.g. operation temperature, radiation hardness and increased ON-resistance.

For the fluorine-implanted HFET, a major concern is the limited long-term stability of the threshold voltage due to fluorine diffusion and the introduction of additional defects in the AlGaN barrier due to the implantation.

Gate-recessed devices require a gate insulator to suppress gate leakage currents. But at the same time, theses gate insulators introduce additional challenges. At the interface between insulator and semiconductor, fixed charges and trap states are formed, which influence the threshold voltage of the devices. Depending on the charge condition at the interface, the insulator can shift the threshold voltage in positive or negative direction, which is either beneficial or detrimental for normally-off operation, respectively. Due to the transient nature of trap states, these effects can also lead to threshold voltage instabilities. Thus, methods to improve this interface are vital for device operation.

Another normally-off topology without a gate insulator is the p-GaN-gated HFET, effectively avoiding the challenges imposed by the insulator/AlGaN interface. In these devices, the 2DEG is depleted by a p-GaN capping layer as long as the AlGaN barrier thickness is below a certain limit. This leads to a trade-off between large positive threshold voltages (thin AlGaN barrier) and low ON-resistances (thick AlGaN barrier). Therefore, it is important to remove the p-GaN outside of the gate area to accumulate the 2DEG without further thinning of the underlying AlGaN. Additionally, this device shows higher gate leakage currents than the insulated-gate devices.

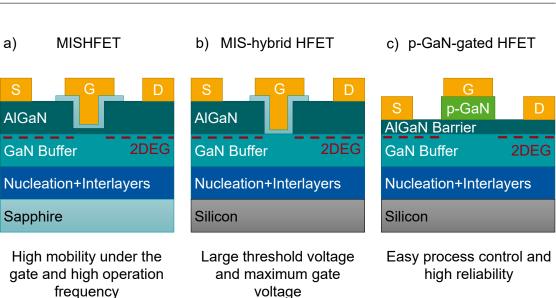

In this work, three out of these five topologies are investigated: the two gate-recessed MISHFET and the p-GaN-gated HFET. Core aspects are analyzed and processes to improve specific device properties are developed. For the two MISHFET, this involves techniques to optimize the insulator/AlGaN interface, while the p-GaN removal and gate module are focal for the p-GaN-gated HFET.

In the following, the structure and content of this work are outlined. First, an intro-

duction into gallium nitride technology, a simple electrostatic model for the electron channel and its relation to the threshold voltage is given. This model is then modified to account for the gate insulator and the insulator/AlGaN interface charge density. In chapter 3, the characterization methods are explained and parameter definitions, particularly for the threshold voltage, are given.

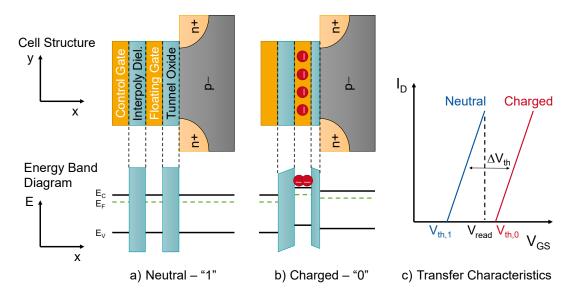

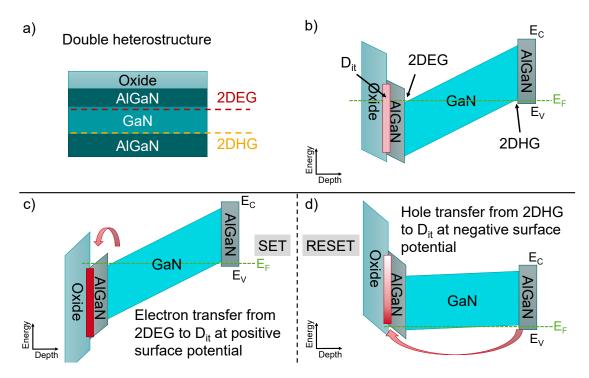

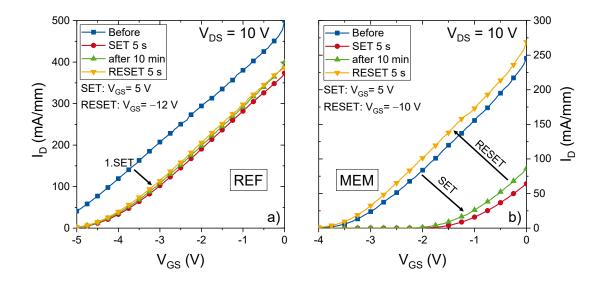

Chapter 4 extends the electrostatic model by interface trap states, which change their charge condition during operation, and it is explained, how these effects impact the device properties of MISHFET. In the following, methods to improve the insulator/semiconductor interface are presented. A gate-recessed device, in which the threshold voltage is shifted in positive direction by the dielectric, is shown and the limitations of this shift are discussed. In the end of this chapter, a memory device concept is shown, which uses the interface trap states as charge storage.

In chapter 5, devices with a completely removed AlGaN barrier, so called MIS-hybrid HFET, are investigated. Due to the removed AlGaN under the gate, the electrons are conducted directly at the insulator/GaN interface which significantly reduces their mobility. To enhance the mobility, an amorphous AlN spike is introduced. For this process, a plasma-enhanced atomic layer deposition (PEALD) method is developed, which is then used for a MIS-hybrid HFET.

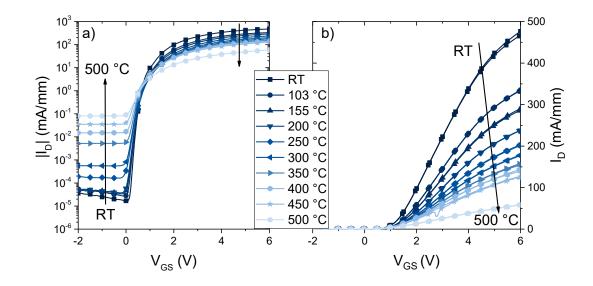

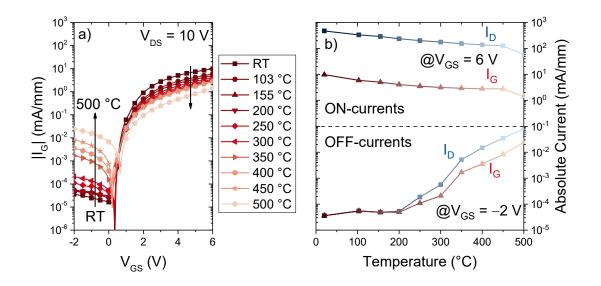

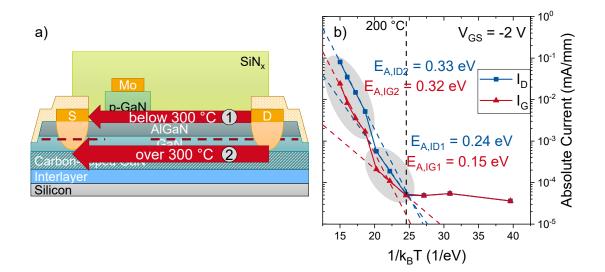

Chapter 6 discusses the p-GaN-gated HFET, its basic working principle and how different parameters influence the threshold voltage. A self-aligned device process with selective removal of the p-GaN cap layer is developed enabling reliable and reproducible manufacturing. Furthermore, elevated-temperature operation of the devices is investigated, since they are particularly suited for this application due to the lack of an insulator. At the end of this chapter, advanced concepts for further performance improvements are introduced and evaluated.

In the final chapter 7, the best suitable application for the different normally-off topologies presented in this work are evaluated.

# 2. Fundamentals of Group III Nitride Technology

This chapter gives a brief introduction to the field of group III nitride semiconductors. First, their crystal structure and relevant properties are discussed. The unique polarization effects of group III nitrides are elaborated, which can be used in heterostructures to form a two-dimensional electron gas (2DEG). An electrostatic model is derived to show the dependence of the sheet carrier density inside the 2DEG on the layer design. Additionally, the scattering mechanisms, which limit the 2DEG electron mobility, are presented.

Afterwards, the working principle of a normally-on heterostructure field-effect transistor (HFET) is explained, how its threshold voltage can be determined from the electrostatic model, and how to achieve normally-off operation. In the end, the impact of a gate dielectric and surface passivation on the device properties is discussed and which parameters of the gate dielectric are important for normally-off HFET.

### 2.1. Crystal Structure

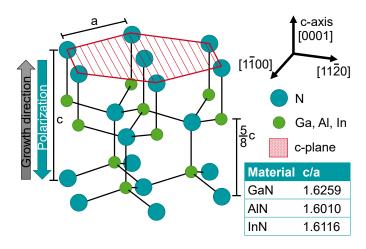

The group III nitrides GaN, AlN and InN can form three different crystal structures, the two cubic structures, zincblende and rocksalt, and the hexagonal wurtzite. The main focus of research and industry is on the thermodynamically-stable wurtzite, which is shown in Fig. 2.1.

A single layer of atoms in this structure consists either of the metal species (Ga, Al, In) or nitrogen. The lattice constant a describes the shortest distance between two atoms of the same layer, whereas the periodicity of the crystal in [0001]-direction is denoted by the lattice constant c. The crystal consists of two hexagonal close-packed arrangements (hcp), one for the metal species and one for nitrogen, which are shifted by 5/8 c in [0001]-direction. In this arrangement, one atom is tetrahedrally coordinated by four atoms of the other element.

**Figure 2.1.:** Crystal structure of the wurtzite structure, typically grown in [0001] direction (metal polar). Blue spheres symbolize nitrogen atoms and the green spheres the metal species [24]. The table shows the c/a ratios for GaN, AlN and InN [25].

For an ideal hcp arrangement, in which all nearest-neighbor bond lengths are equal, the ideal ratio between the lattice constants *c* and *a* is given by  $c_0/a_0 = 1.6330$  [25]. In the case of the group III nitride crystal, this hcp arrangement deviates from the ideal tetrahedral coordination and the wurtzite lacks inversion symmetry. In combination with the ionic character of the bond between metal atom and nitrogen, this results in the largest spontaneous polarization P<sub>sp</sub> among the III-V semiconductors. The structures discussed in this work are all metal polar [26] for which the polarization points downward from top to bottom along the c-axis (in [0001] direction, see Fig. 2.1).

The individual c/a ratios for GaN, AlN and InN are shown in the table of Fig. 2.1. As AlN shows the largest deviation from the ideal c/a ratio ( $c_{AlN}/a_{AlN} = 1.6010$ ) and the Al-N bond has the highest ionicity, it has the strongest P<sub>sp</sub>. The Ga-N bond has the lowest ionicity and is the closest to the ideal c/a ( $c_{GaN}/a_{GaN} = 1.6259$ ), thus it has the weakest P<sub>sp</sub>.

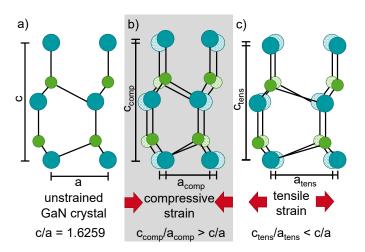

Since  $P_{sp}$  is related to the *c/a* ratio, it is influenced by applied mechanical strain which changes the lattice constants. Fig. 2.2 shows an unstrained (a), a compressively (b) and a tensely biaxially strained crystal (c). In the case of compressive biaxial strain, the lattice constant *a* decreases while lattice constant *c* increases. This brings *c/a* closer to the ideal ratio, which reduces the total polarization. Vice versa, tensile strain increases *a* while decreasing *c*, leading to a higher total polarization. This effect is called piezoelectric polarization  $P_{pz}$  [26].

The total polarization leads to fixed sheet charge densities  $\mp \sigma_x = P_{sp} + P_{pz}$  at the top and bottom c-plane surface of the group III nitride layers, respectively. Consequently, a

**Figure 2.2.:** Impact of mechanical strain on a GaN crystal and its lattice constants. Blue spheres symbolize N atoms and green spheres Ga atoms. a) Unstrained GaN crystal. b) Compressive bi-axial strain increases the c/a ratio (closer to ideal) and therefore decreases the total polarization. c) Tensile biaxial strain lowers the c/a ratio (further away from ideal) which increases the total polarization.

single layer shows an internal electrical field  $\mathcal{E}_x$  in c-direction [27]:

$$\mathscr{E}_{\mathrm{x}} = \frac{\sigma_{\mathrm{x}}}{\varepsilon_{\mathrm{x}}} \tag{2.1}$$

where  $\varepsilon_x$  represents the layer permittivity.

## 2.2. Bandgap and Polarization

As lattice constant *a*, bandgap and polarization are important for predicting device behavior, the theory to calculate these parameters is presented in this section. A high degree of freedom of the group III nitrides originates from the possibility to tune the bandgap and polarization over a wide range. This can be achieved by switching from the binary compounds GaN, AlN and InN to the ternary compounds AlGaN, InGaN, AlInN. They show similar properties to their two binary components, depending on the respective content of each species.

The lattice constant a of ternary compounds can be calculated as a function of its composition x by linear interpolation bet ween the lattice constants of the individual binary compounds. This relation is expressed by Vegard's Law [28]:

$$a_{A_xB_{1-x}N}(x) = a_{AN} \cdot x + a_{BN} \cdot (1-x)$$

(2.2)

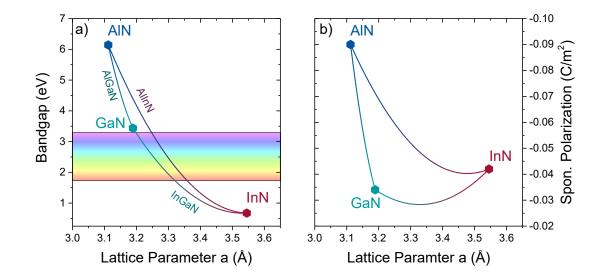

**Figure 2.3.:** Bandgap and the visible spectrum a) and spontaneous polarization b) of the group III nitrides vs. the lattice constant *a*. The points represent the binary compounds and the lines represent the different ternary compounds.

where A and B are the respective metal species of the ternary compound and N stands for nitrogen.

The bandgap and spontaneous polarization as a function of x are estimated by a similar expression with the addition of a bowing parameter b to account for non-linearities [29]:

$$X_{A_xB_{1-x}N}(x) = X_{AN} \cdot x + X_{BN} \cdot (1-x) - b_{ABN} \cdot x(1-x)$$

(2.3)

where X is the bandgap or spontaneous polarization, respectively.

By combining Eq. (2.2) + (2.3), the bandgap and the polarization can be expressed as functions of the lattice constant *a*, which is depicted in Fig. 2.3. The parameters of the binary compounds as well as the respective ternary bowing parameters, which were used in the calculations, are summarized in Tab. 2.1.

Fig. 2.3(a) shows that the InGaN bandgaps cover the entire visible spectrum (indicated by the colored area), which makes this compound particularly interesting for optoelectronic devices [35]. For power and radio-frequency (RF) applications, the wider bandgap and high polarization [see Fig. 2.3(b)] of the Al-containing compounds AlGaN and AlInN on top of a GaN layer are used. This layer combination forms a heterostructure, in which an electron channel can be accumulated without extrinsic doping, the socalled two-dimensional electron gas (2DEG). This is a unique characteristic of group III nitride semiconductors and represents a basic building block for transistors.

| Mat.  | Latt. Par. a | Bandgap | Bandgap Bow. b | Spon. Pol. P <sub>sp</sub> | Pol. Bow. b         |

|-------|--------------|---------|----------------|----------------------------|---------------------|

| Units | (Å)          | (eV)    | (eV)           | (C/m <sup>2</sup> )        | (C/m <sup>2</sup> ) |

| GaN   | 3.189        | 3.438   | -              | -0.034                     | -                   |

| AlN   | 3.112        | 6.140   | -              | -0.090                     | -                   |

| InN   | 3.545        | 0.675   | -              | -0.042                     | -                   |

| AlGaN | -            | -       | 0.94           | -                          | -0.021              |

| InGaN | -            | -       | 2.96           | -                          | -0.037              |

| AlInN | -            | -       | 5.30           | -                          | -0.070              |

**Table 2.1.:** Lattice constant, bandgap and polarization of the binary nitride compounds as well as the bowing parameters for the ternary compounds [29–34].

## 2.3. Heterostructures and the Two-Dimensional Electron Gas

A widely-used heterostructure for electronic devices in the group III nitrides is AlGaN/GaN, in which a thin biaxially strained AlGaN layer is coherently deposited on a relaxed GaN layer (called pseudomorphic growth). The two layers are commonly referred to as AlGaN barrier and GaN buffer, respectively.

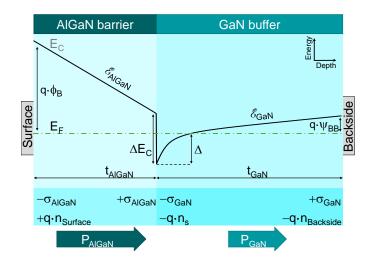

Fig. 2.4 shows the conduction band diagram of an AlGaN/GaN heterostructure and the individual fixed sheet charge densities  $\sigma_x$ , which are related to the polarization. The metal-polar surface of the structure is on the left, while the backside (substrate) is on the right, thus the polarization is directed from left to right. The triangular potential well of the 2DEG, which is populated by the mobile sheet carrier density  $n_s$ , is located at the heterointerface.

To explain the formation of the 2DEG, the derivation of an analytical expression from basic electrostatic equations is presented. This derivation is performed in analogy to [36]. Similar expressions will be used to explain various effects of investigated devices with more complex structures. It will be shown later that the sheet carrier density  $n_s$  is directly connected to the threshold voltage  $V_{th}$  of a HFET, which is the central aspect of this work.

First, Gauss' law is applied to the AlGaN/GaN interface which leads the following expression:

$$\varepsilon_{\text{GaN}}\mathscr{E}_{\text{GaN}} - \varepsilon_{\text{AlGaN}}\mathscr{E}_{\text{AlGaN}} = \sigma_{\text{AlGaN}} - \sigma_{\text{GaN}} - q \cdot n_s$$

(2.4)

This gives the relation of  $n_s$  to the fixed sheet charges  $\sigma_{AIGaN}$  and  $-\sigma_{GaN}$  and the electric

**Figure 2.4.:** Conduction band diagram of an AlGaN/GaN heterostructure, the individual fixed sheet charge densities  $\sigma_x$  and the 2DEG sheet carrier density  $n_s$ .  $\mathcal{E}_{AlGaN}$  and  $\mathcal{E}_{GaN}$  denote the electric fields in the respective layers,  $\Delta E_C$  the conduction band offset between AlGaN and GaN,  $\Delta$  the 2DEG quantum well depth,  $\phi_B$  the surface potential,  $\Psi_{BB}$  the backside potential, and  $t_{AlGaN}$  and  $t_{GaN}$  the respective layer thicknesses.

fields  $\mathscr{E}_{AlGaN}$  and  $\mathscr{E}_{GaN}$  of the AlGaN barrier and GaN buffer, respectively. Here, q is the elementary charge and  $\varepsilon_x$  the respective permittivity.

$\sigma_{AIGaN}$  and  $\sigma_{GaN}$  can be calculated by the theory given in section 2.2, whereas the electric fields are unknown. To determine  $\mathcal{E}_{AIGaN}$  and  $\mathcal{E}_{GaN}$ , two Fermi level reference equations are formulated by following the conduction band edge in the respective layers and considering the surface potential  $\phi_B$  and backside potential  $\Psi_{BB}$ . The quantum well thickness is neglected (« t<sub>GaN</sub>).

For the AlGaN barrier, this leads to the following expression:

$$\phi_{\rm B} - t_{\rm AlGaN} \cdot \mathscr{E}_{\rm AlGaN} - \Delta E_{\rm C}/q + \Delta/q = 0 \tag{2.5}$$

The distance of the conduction band edge to the Fermi level at the surface is expressed by the surface potential  $\phi_B$ . Then, the potential decreases linearly over the AlGaN barrier. The total potential drop is given by the product of the AlGaN barrier thickness  $t_{AlGaN}$  and its electric field  $\mathcal{E}_{AlGaN}$ . At the interface between AlGaN and GaN, the potential is lowered by the conduction band offset  $\Delta E_C/q$  between the two materials. From the bottom of the quantum well, the distance back to the Fermi level is expressed by  $\Delta/q$  [36]:

$$\Delta = \frac{\mathbf{n}_{\rm s} \cdot \pi \hbar^2}{\mathbf{m}^*} \tag{2.6}$$

under the assumption that all electrons within the quantum well occupy the lowest sub-

band [37]. Here, m<sup>\*</sup> represents the effective mass of electrons in GaN.

From there, the expression for the GaN buffer is given by:

$$\mathbf{t}_{\mathrm{GaN}} \cdot \mathscr{E}_{\mathrm{GaN}} - \Psi_{\mathrm{BB}} = 0 \tag{2.7}$$

The potential is linearly increased over the GaN buffer by the product of its thickness  $t_{GaN}$  and its electric field  $\mathscr{E}_{GaN}$  and lowered back to the Fermi level at the backside by the potential  $\Psi_{BB}$ .

The remaining sheet charge densities  $q \cdot n_{Surface}$  and  $-q \cdot n_{Backside}$  ensure charge neutrality:

$$\mathbf{q} \cdot \mathbf{n}_{\text{Surface}} - \mathbf{q} \cdot \mathbf{n}_{\text{Backside}} - \mathbf{q} \cdot \mathbf{n}_{\text{s}} = 0 \tag{2.8}$$

Finally, combining Eq. (2.5) - (2.6) and solving for n<sub>s</sub> leads to the following expression:

$$q \cdot n_{s} = \frac{\sigma_{AlGaN} - \sigma_{GaN} - \frac{\epsilon_{AlGaN}}{t_{AlGaN}} (\phi_{B} - \Delta E_{C}/q) - \frac{\epsilon_{GaN}}{t_{GaN}} \Psi_{BB}}{1 + \frac{\epsilon_{AlGaN}}{t_{AlGaN}} \cdot \frac{\pi\hbar^{2}}{q^{2}m^{*}}}$$

(2.9)

The first part of the equation shows an accumulation term, which is originating from the difference of the fixed sheet charge densities at the AlGaN/GaN interface  $\sigma_{AlGaN} - \sigma_{GaN}$ .

Next, two depletion terms can be identified which reduce  $n_s$ , the front side depletion by the surface potential and AlGaN barrier  $\frac{\epsilon_{AlGaN}}{t_{AlGaN}}(\phi_B - \Delta E_C/q)$  and the backside depletion by the GaN buffer and the backside potential  $\frac{\epsilon_{GaN}}{t_{GaN}}\Psi_{BB}$ . The front side depletion is significant for most of the GaN heterostructure devices, whereas the backside depletion can often be neglected due to thick GaN buffers ( $t_{GaN} \gg 1 \mu m$ , so-called thick-buffer approximation). The denominator accounts for band bending at the AlGaN/GaN interface and has a relatively small effect.

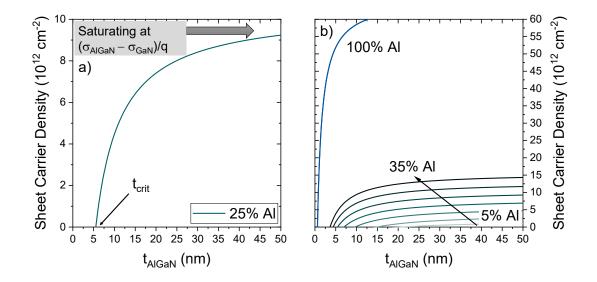

To illustrate the influence of the parameters from Eq. (2.9), Fig. 2.5 displays  $n_s$  calculated for different Al contents and thicknesses of the AlGaN Barrier. Fig. 2.5(a) shows  $n_s$  vs. AlGaN barrier thickness  $t_{AlGaN}$  for a typical Al content of 25%. As apparent from Eq. (2.9), its shape follows the function  $f(t_{AlGaN}) = 1 - 1/t_{AlGaN}$ , which saturates at  $(\sigma_{AlGaN} - \sigma_{GaN})/q$  for  $t_{AlGaN} \rightarrow \infty$  and is zero for  $t_{AlGaN,crit} = 5.4$  nm, i.e. the 2DEG is fully depleted. In the case of small  $t_{AlGaN}$ ,  $n_s$  is more sensitive to variations of  $t_{AlGaN}$ .

For different Al contents in the barrier shown in Fig. 2.5(b), an individual critical thickness  $t_{crit}$  with  $n_{s,Al_xGa_{1-x}N}(t_{crit}) = 0$  and saturation sheet carrier densities can be identified. The higher the Al content in the barrier, the smaller  $t_{crit}$  and the larger  $\sigma_{AlGaN}$  leading to large  $n_s$ .

In real heterostructures, the maximum barrier thickness is limited by the strain in the Al(Ga)N barrier, which is introduced by the lattice mismatch between barrier and buffer.

**Figure 2.5.:** Sheet carrier density vs. AlGaN barrier thickness for different Al contents. a)  $n_s$  vs.  $t_{AlGaN}$  for 25% Al content. Thinner barriers show an increased sensitivity to thickness variations. b) Different  $n_s$  vs.  $t_{AlGaN}$  for Al contents in the range of 5% to 35% in 5% steps and for 100% Al. Parameters for calculating  $P_{sp}$  are shown in Tab. A.1 and calculation of  $P_{pz}$  is performed after [38].  $\phi_B - \Delta E_C/q$  is assumed to be constant as an increase of  $\Delta E_C$  is commonly compensated by an increase in  $\phi_B$  for increasing Al content in the barrier [39].

After a thickness  $t_{relax}$ , barrier relaxation starts which degrades the material quality [26]. As the difference between the lattice constants *a* of barrier and buffer increases with higher Al content (see section 2.2),  $t_{relax}$  decreases leading to an upper limit for  $n_s$ . The maximum reported 2DEG sheet carrier density is  $n_s = 5.5 \cdot 10^{13} \text{ cm}^{-2}$  for an AlN/GaN heterostructure with a 7 nm barrier [40].

#### 2.4. Electron Mobility in the 2DEG

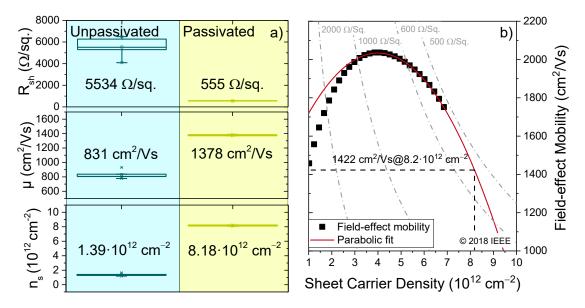

Another distinctive feature of the 2DEG apart from the large sheet carrier density  $n_s$  is its high electron mobility  $\mu$ . Due to the quantization inside the 2DEG potential well and the polarization-induced carriers (without extrinsic doping), the electron mobility can be theoretically increased from 1520 cm<sup>-2</sup>/Vs in bulk GaN up to 2700 cm<sup>-2</sup>/Vs in the 2DEG at room temperature [41].

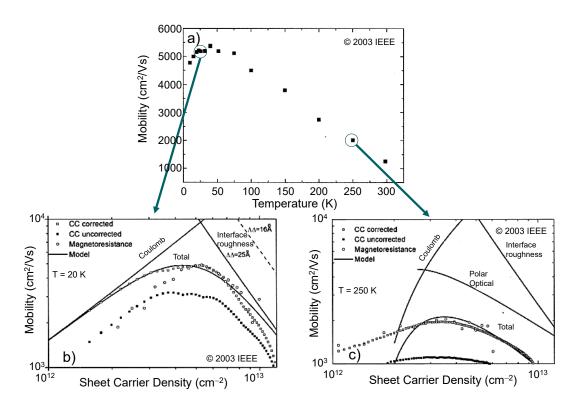

The electron mobility is limited by three dominant scattering mechanisms: Coulomb, interface roughness and optical phonon scattering [37, 42, 43]. In Fig. 2.6,  $\mu$  in dependence of temperature T and n<sub>s</sub> is shown [37]. In Fig. 2.6(a) for T below 77 K, a constant  $\mu$  of about 5200 cm<sup>2</sup>/Vs is observed. Here,  $\mu$  is limited by Coulomb scattering at low n<sub>s</sub> and interface roughness scattering at high n<sub>s</sub> [see Fig. 2.6(b)]. Optical phonon scattering

**Figure 2.6.:** Electron mobility in the 2DEG of an AlGaN/GaN heterostructure. a) Temperature dependence of the electron mobility. b) Sheet carrier density dependence at 20 K. b) Sheet carrier density dependence at 250 K. Images are taken from [37] and slightly modified.

can be neglected here due to low T of 77 K.

Coulomb scattering is caused by ionized impurities and the fixed interface charge densities, which are caused by the polarization. For increasing sheet carrier densities, a part of the free electrons screen the Coulomb field and the impact on  $\mu$  of all free electrons is reduced ( $\mu_{Coul} \propto n_s^2$ ).

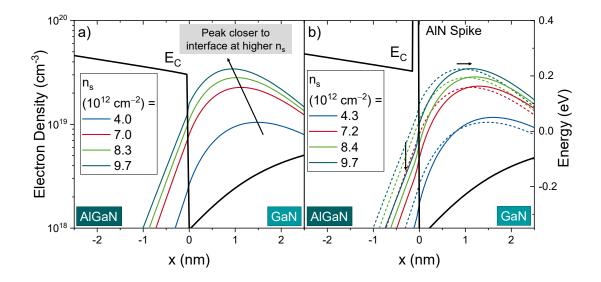

The interface roughness scattering ( $\mu_{IR} \propto n_s^{-2}$ ) in the group III nitrides is based on two different physical properties of the AlGaN/GaN interface: the actual roughness and random fluctuations due to the statistical Al distribution in the AlGaN barrier, the so-called alloy disorder scattering [44]. To understand the dependence of the interface roughness scattering on  $n_s$ , Fig 2.7(a) shows bulk electron density depth profiles for different  $n_s$  simulated by an 1D Poisson solver [45]. Additionally, the conduction band edge of the simulated AlGaN/GaN structure with the highest  $n_s$  is shown as an orientation. For increasing  $n_s$ , the quantum well of the 2DEG becomes energetically deeper (not shown here), which moves the centroid of the bulk electron density closer to the interface. Therefore, more electrons are scattered by the interface roughness and by alloy disorder, leading to a reduced  $\mu$  in the 2DEG [42].

**Figure 2.7.:** Electron density profiles for different  $n_s$ . The conduction band edge is shown as orientation. a) AlGaN/GaN heterostructure. For higher values of  $n_s$ , the peak of the profile is shifted towards the interface. b) AlGaN/AlN/GaN heterostructure. Due to the AlN spike, the peak is shifted away from the interface and the electron density inside the barrier is reduced.

A method to mitigate this effect is the introduction of a very thin AlN spike between AlGaN barrier and GaN channel [46]. Fig. 2.7(b) shows the difference between the electron density profiles from Fig. 2.7(a) (dashed lines) and a simulated AlGaN/AlN/GaN structure (solid lines) for similar  $n_s$ . The AlN spike increases the AlGaN/GaN conduction band offset leading to a higher potential barrier for the electrons in the 2DEG. Therefore, the confinement of the electrons to the quantum well increases, which shifts the centroid away from the interface. Additionally, the electron density located inside the AlGaN is reduced. Furthermore, AlN as binary compound does not show random fluctuations in the composition, which reduces alloy disorder scattering. These two effects lead to an overall increase of  $\mu$  at high  $n_s$ .

The main limiting factor for temperatures above 77 K is optical phonon scattering, which has an exponential temperature dependence [see Fig. 2.6(a)] [37]. This scattering mechanism is caused by the interaction of the electrons with the Coulomb field of the lattice polarization waves of polar semiconductors. However, the mobility is still affected by Coulomb and interface roughness scattering for low and high  $n_s$ , respectively [Fig. 2.6(c)]. Therefore, the reduction of interface roughness scattering is mandatory to achieve high mobilities at high carrier densities.

#### 2.5. Heterostructure Field-Effect Transistor

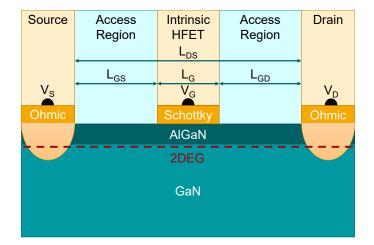

The heterostructures with its key features, high sheet carrier density and electron mobility, from the previous section will now be employed in a heterostructure field-effect transistor (HFET). This device is depicted in Fig. 2.8 with ohmic source and drain contacts as well as Schottky gate contact.

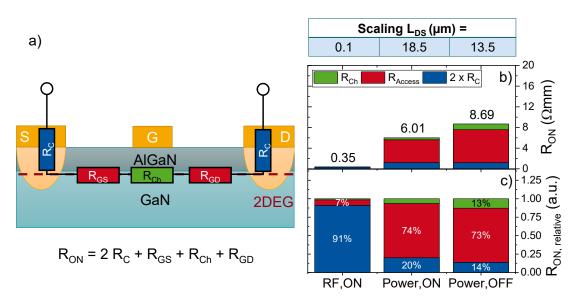

The HFET can be divided into two regions: The intrinsic HFET under the gate electrode, which is responsible for the control of the conductive channel, and the access regions, which separate the source and drain from the gate.

The intrinsic HFET is shown in the center. It consists of the heterostructure with a gate metal on top of the AlGaN barrier. This system represents a plate capacitor with gate metal and 2DEG as plates and the AlGaN barrier as dielectric. By applying a gate voltage, the sheet carrier density  $n_s$  in the 2DEG can be modified [47]. The gate voltage  $V_{GS}$  in the electrostatic model is accounted for by an additional term in Eq. (2.9). It modifies the surface potential  $\phi_B$  and leads to the following expression:

$$q \cdot n_{s} = \frac{\sigma_{AlGaN} - \sigma_{GaN} - \frac{\epsilon_{AlGaN}}{t_{AlGaN}}((\phi_{B} - \mathbf{V}_{GS}) - \Delta E_{C}/q) - \frac{\epsilon_{GaN}}{t_{GaN}}\Psi_{BB}}{1 + \frac{\epsilon_{AlGaN}}{t_{AlGaN}} \cdot \frac{\pi\hbar^{2}}{q^{2}m^{*}}}$$

(2.10)

Since the surface potential is now defined by the gate metal,  $\phi_B$  is referred to as Schottky barrier height between metal and semiconductor. Positive V<sub>GS</sub> increases n<sub>s</sub>, while

**Figure 2.8.:** Schematic of an AlGaN/GaN heterostructure field-effect transistor (HFET). The intrinsic HFET consists of the gate area which is responsible for the control of the device. The drain and source contacts are typically separated from the intrinsic HFET by the access regions. The relevant geometries are the drain-source distance  $L_{DS}$ , the gate length  $L_G$ , the gate-source distance  $L_{GS}$  and gate-drain distance  $L_{GD}$ .

negative  $V_{GS}$  decreases  $n_s$ .

The threshold voltage  $V_{th}$  for full depletion of  $n_s$  and therefore switching off the transistor can be extracted from Eq. (2.10) by setting  $n_s = 0$  and solving for  $V_{GS}$ :

$$V_{th} = V_{GS} = \phi_B - \Delta E_C / q - \frac{t_{AIGaN}}{\epsilon_{AIGaN}} (\sigma_{AIGaN} - \sigma_{GaN}) + \frac{t_{AIGaN}}{t_{GaN}} \cdot \frac{\epsilon_{GaN}}{\epsilon_{AIGaN}} \cdot \Psi_{BB}$$

(2.11)

With the thick-buffer approximation ( $t_{GaN} \gg 1 \ \mu m \gg t_{AlGaN}$ ), the expression above simplifies to:

$$V_{th} = \phi_B - \Delta E_C / q - \frac{t_{AIGaN}}{\epsilon_{AIGaN}} (\sigma_{AIGaN} - \sigma_{GaN})$$

(2.12)

Thicker AlGaN barriers and higher polarization differences between AlGaN and GaN lead to more negative  $V_{th}$  as they increase  $n_s$  at zero bias (cf. section 2.3).

Typical HFET with 25% Al content, 20 nm barrier thickness and a Ni gate [48, 49] have a calculated  $V_{th}$  of -2.7 V. This HFET will be taken as a reference to illustrate the influence of the parameters above on  $V_{th}$ . Due to the negative  $V_{th}$ , these HFET are classified as normally-on devices, i.e. they are in ON-state at zero gate bias.

For circuit design, not only normally-on but also normally-off transistors, i.e. transistors with a positive  $V_{th}$ , are needed. The advantages of normally-off HFET are the elimination of a negative-voltage supply requirement and OFF-state of the device in case of gate driver malfunctioning, which is necessary for power applications. Additionally, access to both, normally-on and normally-off devices, enables complementary designs, e.g. more efficient push-pull inverters [50] or cascodes [51].

This work focuses on the major normally-off concepts of group III nitride HFET. The impact of device design on  $V_{th}$  is presented, the individual  $V_{th}$  limitations are given and how certain aspects of such devices can be improved. The general approach for all of these concepts is the depletion of the 2DEG in the intrinsic HFET at zero gate bias, while maintaining the key features of the heterostructure: high electron mobilities throughout the whole device and high 2DEG sheet carrier densities in the access regions.

From Eq. (2.11), it is evident that three degrees of freedom exist to tune  $V_{th}$ : the Schottky barrier height  $\phi_B$  which is dependent on the gate metal, and the AlGaN barrier with its polarization, which is dependent on the Al content, and its thickness.

To achieve a large  $\phi_B$ , which increases V<sub>th</sub>, a gate metal with a high work function is chosen. The gate contact metal for the AlGaN/GaN HFET in this work is Ni with a work function of 5.1 eV, which is capped by an Au layer. This represents a common gate metalization for GaN HFET [9,17,39,52,53]. The metal with the highest work function available is Pt with 5.65 eV [54], thus only a minor V<sub>th</sub> shift to more positive voltages is possible [55]. By exchanging the Ni gate with a Pt gate in the example above,  $V_{th}$  would be shifted from -2.70 V to -2.15 V in an ideal case. Consequently, the AlGaN barrier is the most important design element for achieving normally-off operation.

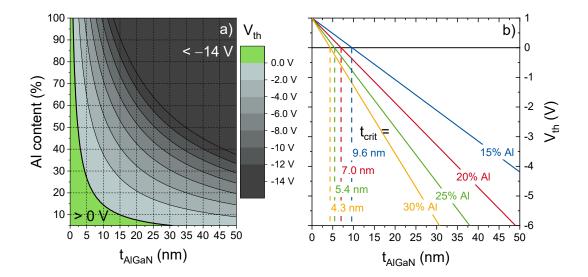

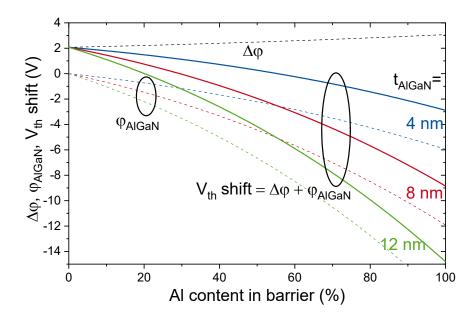

Fig. 2.9 shows the dependence of  $V_{th}$  on the AlGaN barrier thickness and composition, under the assumption that  $\phi_B - \Delta E_C = 1 \text{ eV} = \text{const.}$  for varying Al contents [26, 36, 39]. The green area in Fig. 2.9(a) shows the normally-off regime, in which  $V_{th} > 0 \text{ V}$  is achieved. Increasing the Al content in the barrier decreases the thickness  $t_{crit}$ , which is the maximum thickness that allows for normally-off operation. In the case of the example HFET with 25% Al content, a reduction of the barrier thickness below  $t_{crit} = 5.4 \text{ nm}$  would be necessary. For an AlN barrier (100% Al),  $t_{crit}$  is approximately 1 nm.

In conclusion, normally-off HFET can be achieved by a low Al content and/or a thin AlGaN barrier. Reduction of the AlGaN barrier thickness is the better solution for two reasons: Reducing th Al content would also lower the conduction band offset at the Al-GaN/GaN interface, which decreases the electron mobility due to inferior confinement in the 2DEG (see section 2.4). Secondly, the high carrier density and mobility need to be retained in the access regions. Thus, the normally-off modification has to be limited to the intrinsic HFET, i.e. the gate area. As the heterostructure is grown in a conventional epitaxial process [56], intentional lateral variations of the Al content cannot be achieved during a single growth process. On the other hand, the barrier can be locally thinned by

**Figure 2.9.:** Threshold voltage as a function of AlGaN barrier thickness and Al content. a) Contour plot of  $V_{th}$  vs. Al content and  $t_{AlGaN}$ . b)  $V_{th}$  vs.  $t_{AlGaN}$  for four different Al contents.  $t_{crit}$  denotes the barrier thickness for which normally-off operation is achieved.

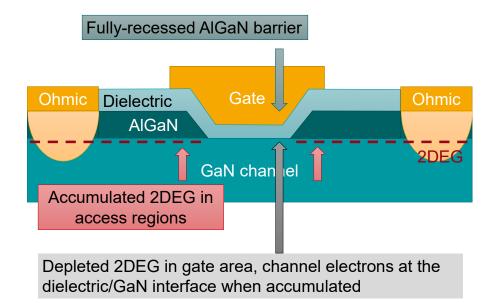

**Figure 2.10.:** Schematic of a passivated MISHFET and the corresponding conduction band diagram. New parameters in regard to Fig. 2.4 are the conduction band offset between dielectric and AlGaN  $\Delta E_{C,ins}$ , the dielectric thickness  $t_{ins}$  and the interface charge density  $\sigma_{int}$ .

patterned dry-etching during device processing [17], the so-called gate-recess etching. This leads to a high electron mobility and a vanishing/high sheet carrier density in the intrinsic HFET and access regions, respectively.

#### 2.6. Dielectrics in an HFET

In contrast to a MOSFET, the basic functionality of the HFET requires no dielectric as the AlGaN barrier serves as an insulator between gate metal and 2DEG. Nonetheless, dielectrics are mandatory for real devices to mitigate parasitic effects.

#### 2.6.1. Electrostatics of a MISHFET

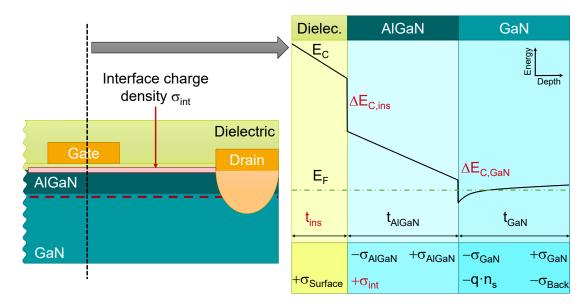

Due to the introduction of a dielectric, the electrostatics described in the previous sections change. The new structure and extended band diagram are shown in Fig. 2.10. Additional parameters are the conduction band offset between dielectric and AlGaN  $\Delta E_{C,ins}$ , the dielectric thickness t<sub>ins</sub> and an interface charge density  $\sigma_{int}$ . A derivation similar to Eq. (2.9) can be performed leading to the following expression [36]:

$$\begin{aligned} \mathbf{q} \cdot \mathbf{n}_{s} &= \left[ \boldsymbol{\sigma}_{AIGaN} - \boldsymbol{\sigma}_{GaN} - \frac{1}{\frac{t_{AIGaN}}{\epsilon_{AIGaN}} + \frac{t_{ins}}{\epsilon_{ins}}} (\boldsymbol{\phi}_{B} - \Delta E_{C,ins}/q - \Delta E_{C,GaN}/q) \right. \\ &- \frac{\frac{t_{ins}}{\epsilon_{AIGaN}}}{\frac{t_{AIGaN}}{\epsilon_{AIGaN}} + \frac{t_{ins}}{\epsilon_{ins}}} (\boldsymbol{\sigma}_{AIGaN} - \boldsymbol{\sigma}_{int}) \\ &- \frac{\epsilon_{GaN}}{t_{GaN}} \Psi_{BB} \right] \\ &- \left[ 1 + \frac{1}{\frac{t_{AIGaN}}{\epsilon_{AIGaN}} + \frac{t_{ins}}{\epsilon_{ins}}} \cdot \frac{\pi\hbar^{2}}{q^{2}m^{*}} \right] \end{aligned}$$

(2.13)

Here, the barrier capacitance ( $\epsilon_{AlGaN}/t_{AlGaN}$ ) is substituted by the series capacitance of the barrier capacitance and the dielectric capacitance ( $t_{AlGaN}/\epsilon_{AlGaN}+t_{ins}/\epsilon_{ins}$ )<sup>-1</sup>. Furthermore, a term accounting for the dielectric is introduced (second row in Eq. (2.13)).

The interface charge density  $\sigma_{int}$  is the most important new variable, as it defines the dependence of  $n_s$  on the properties of the dielectric. In the case of  $\sigma_{AlGaN} - \sigma_{int} = 0$ , i.e. a charge-neutral interface between AlGaN and passivation, the corresponding dielectric term drops out of the equation. The only difference to the dielectric-free equation Eq. (2.9) is now the substitution of the barrier capacitance. In this case, increasing the barrier thickness  $t_{AlGaN}$  has a similar effect on  $n_s$  as increasing the dielectric thickness  $t_{ins}$ . For  $\sigma_{AlGaN} - \sigma_{int} < 0$ , the dielectric term has a positive sign leading to a higher  $n_s$ .

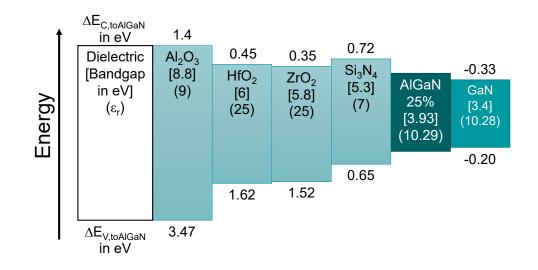

Apart from  $\sigma_{int}$ , the band alignment  $\Delta E_{C,ins}$  between dielectric and barrier and the permittivity have to be taken into account. Fig. 2.11 shows different dielectrics, which are currently investigated in nitride technology [57–60], and their parameters in relation to an AlGaN barrier with 25% Al. The focus of this work is on silicon nitride (SiN<sub>x</sub>) as surface passivation and aluminum oxide (AlO<sub>x</sub>) as gate dielectric. SiN<sub>x</sub> has proven to be one of the best surface passivation materials [36, 53, 64, 65] in group III nitride technology. AlO<sub>x</sub> has one of the best insulating properties with a conduction band offset of 1.4 eV and a medium relative permittivity of 9.

In this work, only the interface charge density  $\sigma_{int}$  is considered. Commonly, dielectrics also have bulk volume charge densities [66], which are important if dielectrics with different thicknesses are investigated. Here, the dielectric thickness is kept constant during each experiment and the bulk charge densities are integrated into the interface charge density  $\sigma_{int}$ .

A more detailed explanation of the impact of the dielectrics on the device properties

**Figure 2.11.:** Schematic of calculated band offsets of different dielectrics to AlGaN with 25% Al. Parameters of the dielectrics are taken from [61], whereas the AlGaN and GaN parameters are calculated. Image designed after [62, 63].

is given the following sections, starting with the surface passivation.

#### 2.6.2. Surface Passivation of the Access Regions

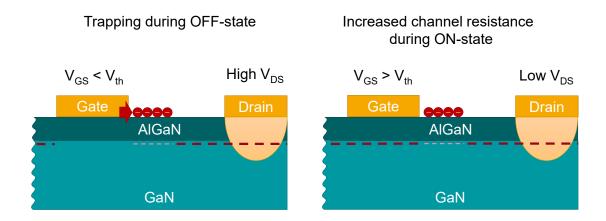

In the access regions, the surface is not covered by a metal layer. Therefore, the surface potential is not fixed and can be influenced by absorbed ions or captured charge carriers in surface states. These surface states are originating from the abrupt end of the bulk semiconductor, which leads to unsaturated bonds (dangling bonds) and defects in the crystal structure. In the case of nitride semiconductors, the surface is particularly prone to capture electrons due to polarization [67].

In an HFET during device OFF-state at high drain bias, the gate metal edge emits electrons into these surface states (depicted in Fig. 2.12). The negative surface potential built up by the trapped electrons then leads to a depletion of the 2DEG. When the device is switched to ON-state, these electrons are not immediately discharged and lead to an increases resistance of the access regions. This effect is called virtual gating as the negative surface potential acts like a gate with negative bias [67]. A technique to mitigate virtual gating is surface passivation. By depositing a dielectric on top of the AlGaN barrier, a majority of the surface traps are saturated. Furthermore, the actual device surface is shifted away from the 2DEG, which reduces its influence on  $n_s$  [see Eq. (2.9)]. Here, the focus is not on the insulating properties, but on a dielectric/AlGaN interface with low trap densities and fast discharging of trapped electrons during switching.

**Figure 2.12.:** Virtual gating effect during OFF-state. Electrons are emitted from the gate edge and trapped in surface states on top of the AlGaN barrier. The negative surface potential depletes the 2DEG leading to an increased channel resistance during the ON-state.

In addition to the reduced virtual gating, the experimental results using silicon nitride passivation show an increased  $n_s$ . This effect is expected from the electrostatic model of Eq. (2.13) for  $\sigma_{AlGaN} - \sigma_{int} \leq 0$  and is particularly beneficial for HFET with thin AlGaN barriers, since  $n_s$  can be increased in the access regions by the passivation leading to an improved  $R_{ON}$ .

However even in a passivated device, charge trapping can occur at the SiN/barrier interface. The trapped electrons reduce  $\sigma_{int}$ , which increases the difference  $\sigma_{AlGaN} - \sigma_{int}$  and decreases  $n_s$ . Thus, the passivation should have a positive fixed charge  $\sigma_{int}$  greater than  $\sigma_{AlGaN}$  and ideally, no electron traps at the interface.

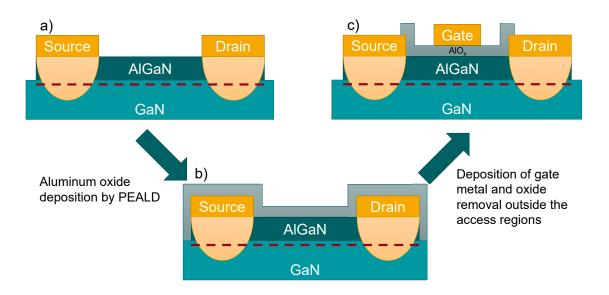

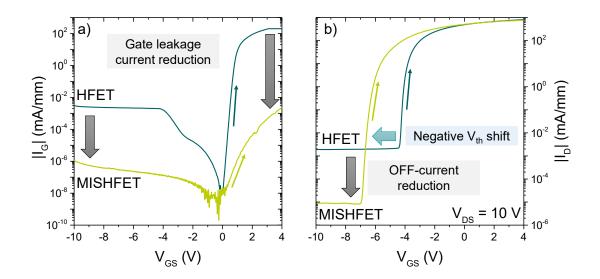

#### 2.6.3. Gate Insulation of the intrinsic HFET

In the intrinsic HFET, the gate leakage current can be reduced by switching to a metal-insulator-semiconductor HFET (MISHFET). This is particularly important for normally-off devices, which are realized by gate-recess etching. Due to the thin barrier, the leakage current is increased in comparison to the normally-on HFET. Additionally, the gate diode of the HFET is no longer biased in reverse direction to deplete the 2DEG, but needs to be biased in forward direction for 2DEG accumulation. This leads to high gate leakage currents during the device ON-state [17]. The additional dielectric of the MIS contact is able to suppress these leakage currents.

The requirements for an optimal gate insulator are a large bandgap with a conduction band offset over 1 eV to the barrier for electron blocking capabilities at positive gate bias, low bulk defect densities and a high quality interface between the insulator and semiconductor [68].

The strongest impact of the dielectric on the device characteristics of the intrinsic HFET, is the threshold voltage shift  $\Delta V_{th}$ . Solving Eq. (2.13) for the threshold voltage in analogy to section 2.5 gives the following equation:

$$V_{th} = \phi_B - \Delta E_{C,ins}/q - \Delta E_{C,GaN}/q - \frac{t_{AIGaN}}{\epsilon_{AIGaN}}(\sigma_{AIGaN} - \sigma_{GaN}) - \frac{t_{ins}}{\epsilon_{ins}}(\sigma_{int} - \sigma_{GaN})$$

(2.14)

The threshold voltage is now not only defined by the AlGaN barrier, but also by the insulator thickness and the interface charge  $\sigma_{int}$ .

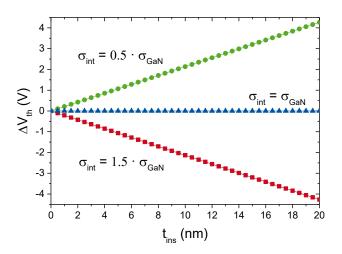

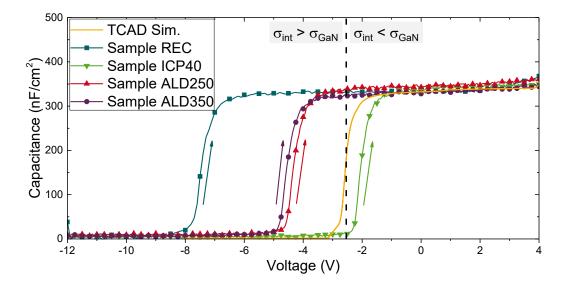

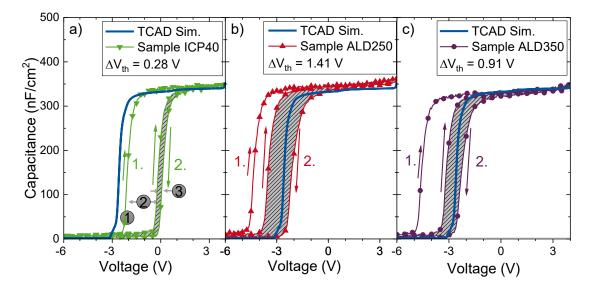

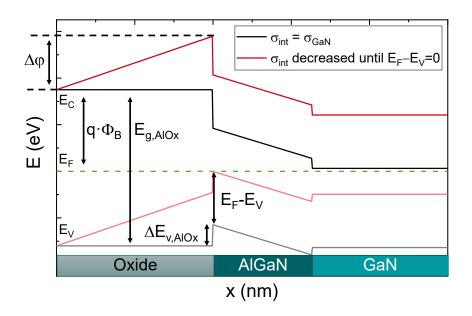

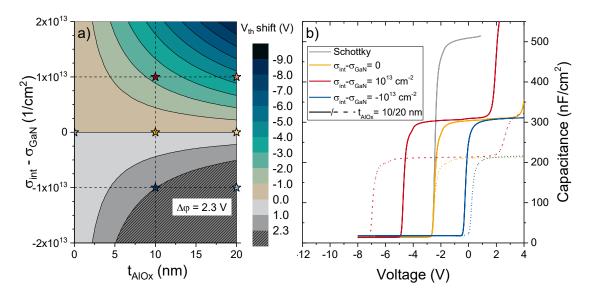

For the threshold voltage dependence on the insulator properties, it can be differentiated between three cases in analogy to Eq. (2.13). They are shown in Fig. 2.13: In the first case  $\sigma_{int} = \sigma_{GaN}$ , the term equals zero and no  $\Delta V_{th}$  occurs. For  $\sigma_{int} > \sigma_{GaN}$ ,  $V_{th}$  is shifted to more negative values with increasing insulator thickness, whereas for  $\sigma_{int} < \sigma_{GaN}$ ,  $V_{th}$  is shifted to more positive values.

**Figure 2.13.:** Threshold voltage shift  $\Delta V_{th}$  in dependence of the insulator thickness  $t_{ins}$ . The plot shows three different cases for the interface charge density  $\sigma_{int}$ :  $\sigma_{int} < \sigma_{GaN}$ ,  $\sigma_{int} = \sigma_{GaN}$  and  $\sigma_{int} > \sigma_{GaN}$ .

Therefore, the gate dielectric can have a large impact on the operation mode of the device. In case of a positive  $V_{th}$  shift, the dielectric is beneficial for the normally-off HFET as it shifts  $V_{th}$  to even more positive voltages or can enable normally-off operation with thicker AlGaN barriers. In case of the negative  $V_{th}$  shift however, the dielectric can turn the initially normally-off HFET into a normally-on MISHFET. Thus, the control of  $\sigma_{int}$  is particularly critical for normally-off devices.

In this chapter, an introduction into the group III nitrides was given. The uniquelyhigh polarization effects can be used in heterostructure to create a conducting channel, the 2DEG, without doping. The electrostatics of the heterostructure were explained and it was shown that the AlGaN barrier composition and thickness have the highest impact on the sheet carrier density inside the 2DEG. In addition, the 2DEG also shows a high electron mobility, for which the main scattering mechanisms and limitations were introduced. Based on this heterostructure with its two key features, high sheet carrier density and electron mobility, the HFET was explained with focus on its threshold voltage. A method to shift the threshold voltage from negative to positive was shown, i.e. turning a normally-on into a normally-off device through thin barriers. In the last part, the requirement for dielectrics in a normally-off HFET and their impact on the device properties, particularly the impact on  $V_{th}$ , was explained.

# 3. Electrical Characterization Methods

In this chapter, the characterization methods for the different device properties are presented and the corresponding measurements plots explained. Capacitance-Voltage (C-V) profiling is a powerful tool to investigate the heterostructures in terms of electron density  $n_s$ , interface charge density  $\sigma_{int}$  and threshold voltage  $V_{th}$ . Current-voltage (I-V) measurements are used to characterize the manufactured HFET and extract its relevant parameters. Pulsed-I-V gives access to analyzing dispersive behavior which is only visible through switching between stress and measurement bias points.

#### 3.1. Capacitance-Voltage (C-V)

Capacitance-Voltage (C-V) profiling enables a profound investigation of the accumulation and depletion processes in nitride heterostructures. The underlying principle of C-V measurements is a small-signal alternating-current (AC) excitation of charge carriers and the measurement of the total transported charge. From the two parameters, a corresponding capacitance can be extracted. In C-V profiling, this measurement is performed for different direct-current (DC) bias points. This allows for analyzing the depletion or accumulation of charge carriers depending on their polarity as well as their depth profiles.

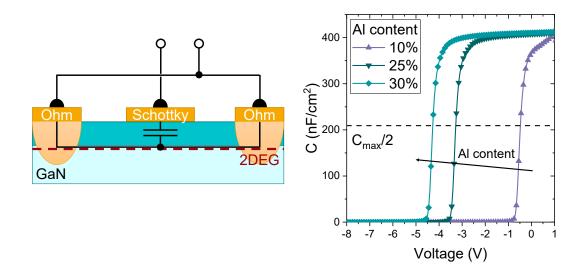

Fig. 3.1 depicts a schematic of an AlGaN/GaN heterostructure with a simple equivalent circuit. The cross section contains a large-area diode (LAD, see A.5) used for the C-V measurements and the plot shows simulated C-V curves. The simulations are performed for a 20 nm AlGaN barrier with varying Al content in Sentaurus TCAD [69]. The measured capacitance equals a plate capacitor with the Schottky contact as one plate and the 2DEG as the other with AlGaN as dielectric:

$$C = \varepsilon_0 \varepsilon_r \cdot \frac{A}{t_{AlGaN}}$$

(3.1)

**Figure 3.1.:** Schematic of an AlGaN/GaN heterostructure with a simple equivalent circuit and simulated C-V plots of the device. The simulations are performed for a 20 nm AlGaN barrier with varying Al content.

where A is the device area (Schottky area for a LAD) and t<sub>AlGaN</sub> the AlGaN thickness.

On the left side of the C-V plots, towards negative DC bias voltage, the 2DEG is depleted and therefore  $C = 0 \text{ nF/cm}^2$ . At some point, the capacitance rises and saturates when the 2DEG is fully formed. The threshold voltage V<sub>th</sub> for the LAD is defined at the point on which half of the maximum capacitance  $C_{max}/2$  is reached. As described in the previous section, the varying of the Al content inside the barrier changes the polarization difference and therefore shifts V<sub>th</sub>. The slight increase in capacitance after V<sub>th</sub> towards zero is originating from a shift in the electron density maximum towards the AlGaN barrier for higher carrier concentrations (see section 2.4). The 10% Al content curve rises faster in the accumulation regime because of the weak carrier confinement due to only a small conduction band offset between AlGaN and GaN. In the positive bias regime, the Schottky gate contact becomes conductive and the leakage current invalidates the C-V measurement. This limits the measurement to approximately 1 V.

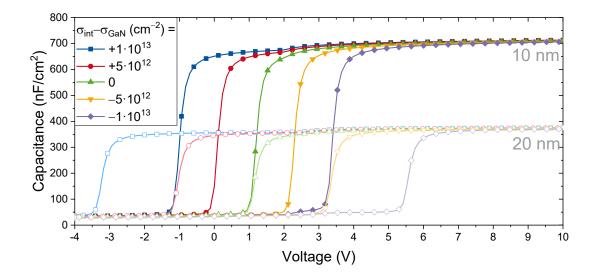

For a MISHFET device, an additional gate insulator is deposited on top of the AlGaN barrier. In the accumulated 2DEG state, a series capacitance of AlGaN and insulator is now measured:

$$C = \frac{C_{\text{ins}} \cdot C_{\text{AlGaN}}}{C_{\text{ins}} + C_{\text{AlGaN}}}$$

(3.2)

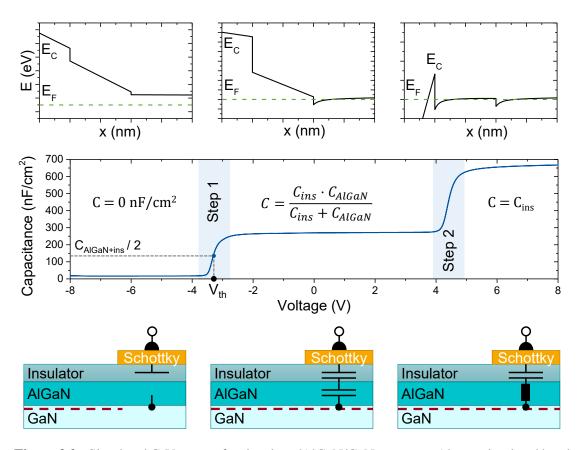

Furthermore, a third state in the C-V curve other than 2DEG accumulation and depletion can be observed, the so-called spill-over regime [70]. The different regimes with the corresponding equivalent circuits are depicted in Fig. 3.2. Under larger forward bias of

**Figure 3.2.:** Simulated C-V curve of an insulator/AlGaN/GaN structure. Above, simulated band diagrams for the different states are shown whereas below, the corresponding equivalent circuits are depicted.

the gate diode, the electrons are able to surpass the AlGaN barrier and are transfered from the 2DEG to the insulator/AlGaN interface. The capacitance rises and now only the insulator capacitance is measured, which is connected to the 2DEG over the AlGaN barrier resistance.

The visibility of this second capacitance plateau after step 2 is dependent on the measurement frequency and AlGaN barrier resistance [70]. In a quasi-static C-V measurement, the second plateau is always visible, whereas it can be suppressed at higher frequencies due to the  $R_{AlGaN} \cdot C_{ins}$  time constant of barrier and insulator. For large time constants, the electrons at the insulator/AlGaN interface cannot follow the applied AC signal and therefore, only the series capacitance of oxide and barrier is measured in the spill-over regime. Thus, it is beneficial for the C-V characterization to measure at lower frequencies.

Furthermore, the MIS theory of Eq. (2.14) is also valid in this case. By solving this

equation for  $\sigma_{int}$ , it can be determined from V<sub>th</sub> extracted at C<sub>AlGaN+ins</sub>/2:

$$\sigma_{\text{int}} = \frac{\varepsilon_{\text{ins}}}{t_{\text{ins}}} \cdot \left[\phi_{\text{B}} - \Delta E_{\text{C,ins}}/q - \Delta E_{\text{C,GaN}}/q - V_{\text{th}} - \frac{t_{\text{AlGaN}}}{\varepsilon_{\text{AlGaN}}}(\sigma_{\text{AlGaN}} - \sigma_{\text{GaN}})\right] + \sigma_{\text{GaN}}$$

(3.3)

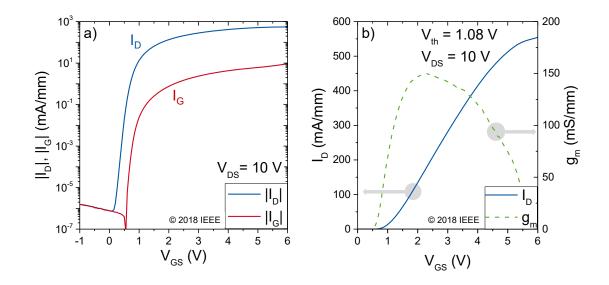

### 3.2. Current-Voltage (I-V)

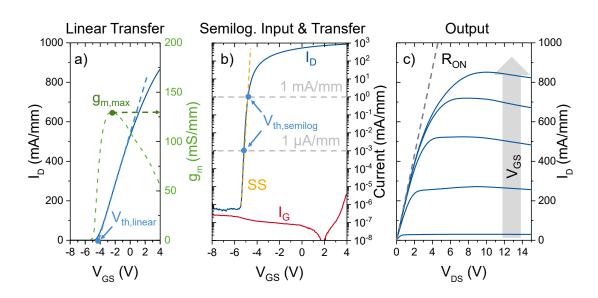

For the basic characterization of transistors, commonly three different direct current-voltage (I-V) measurements are employed as shown in Fig. 3.3:

- Input characteristics which describe the gate current in dependence of the gatesource voltage I<sub>G</sub> vs. V<sub>GS</sub>.

- Output characteristics which show the drain current in dependence of the drainsource voltage I<sub>D</sub> vs. V<sub>DS</sub> at constant V<sub>GS</sub>.

- Transfer characteristics which contain the drain current in dependence of the gatesource voltage I<sub>D</sub> vs. V<sub>GS</sub> at constant V<sub>DS</sub>.

From the transfer characteristic in linear scale in Fig. 3.3(a),  $V_{th}$  can be estimated by linear extrapolating the tangent in the point of maximum transconductance  $g_{m,max}$ towards the x-Axis. The value of  $g_{m,max}$  is an important characteristic for the switching behavior of the transistor, since it shows how effectively the output current  $I_D$  can be controlled by the input voltage  $V_{GS}$ .

Fig. 3.3(b) shows a semilogarithmic plot of the transfer characteristic (blue) as well as the input characteristic (red). From the plot, several electrical properties can be extracted. At negative voltages, the flat line of the current represents the OFF-current of the device and is responsible for the OFF-state power dissipation.

Furthermore, the sub-threshold swing SS can be estimated from the slope of the drain current curve below  $V_{th}$  and is given in millivolt  $V_{GS}$  per decade  $I_D$  (mV/dec). A lower value shows a better current control, and is physically limited to a minimum of 60 mV/dec at room temperature [71] for conventional field-effect transistors.

Two additional threshold voltage criteria are defined at a constant current of 1 mA/mm and 1  $\mu$ A/mm for a soft- and hard OFF-state, respectively. Since the electrostatic theory for V<sub>th</sub> assumes a sheet carrier density of zero [see Eq. (2.11)], the hard OFF-state V<sub>th</sub> is the most suitable criterion for comparison of theoretical and experimental values.

The output characteristics are shown in Fig. 3.3(c). The plot depicts  $I_D$  vs.  $V_{DS}$  curves for different fixed  $V_{GS}$  values. The current rises linearly for low  $V_{DS}$  (linear regime) and eventually saturates at higher values (saturation). For high  $I_D$  and  $V_{DS}$ , the curve is

**Figure 3.3.:** Input, output and transfer characteristics of an example MISHFET. a) Transfer characteristics in linear scale (blue) with the corresponding transconductance (green).  $V_{th}$  can be estimated by linear extrapolation of the tangent in the point of maximum transconductance  $g_{m,max}$  towards the x-axis. b) Input (red) and transfer characteristics (blue) in semilogarithmic scale. Two threshold voltage criteria are defined at a constant current of 1 mA/mm and 1  $\mu$ A/mm for a soft- and hard OFF-state, respectively. The sub-threshold swing SS is estimated from the slope of the drain current curve below  $V_{th}$  (orange). c) Output characteristic in linear scale. The ON-resistance  $R_{ON}$  is calculated from  $V_{DS}$  at  $I_D = 100$  mA/mm for the curve with the highest  $V_{GS}$ .

declining due to self-heating of the device. From the linear regime, the ON-resistance  $R_{ON}$  of the device can be extracted. Commonly,  $V_{DS}$  at  $I_D = 100 \text{ mA/mm}$  is extracted for the curve with the highest  $V_{GS}$  and the resistance times gate width is calculated (values in  $\Omega$ mm).  $R_{ON}$  is an important parameter for power electronics since it is a major contributor to losses and should be as low as possible.

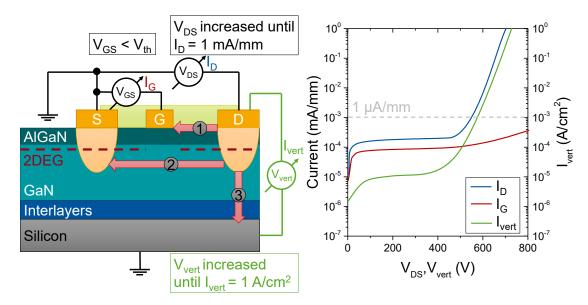

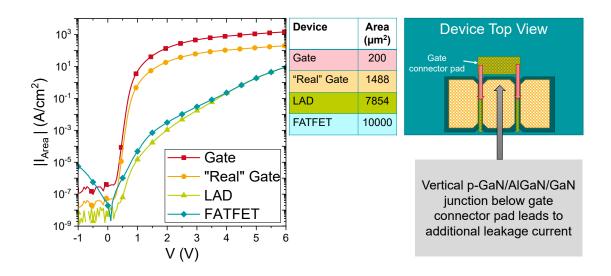

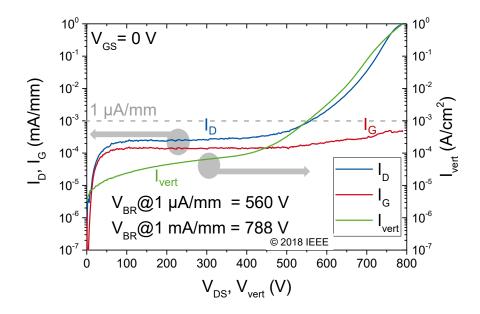

#### Three-Terminal- and Vertical Breakdown

Breakdown measurements are performed to estimate the maximum operation voltage of electrical devices. Fig. 3.4 shows a schematic cross section of an HFET and example measurement curves. The upper limit can be either given by a lateral- or a vertical current flow and is extracted by two different types of measurement. First, a three-terminal breakdown measurement is performed in which the HFET is kept in OFF-state ( $V_{GS} < V_{th}$ ) and  $V_{DS}$  is steadily increased until a drain current I<sub>D</sub> of 1 mA/mm is reached (soft breakdown criterion). Additionally, the gate current is measured while the substrate is grounded. During the measurement, the probes and DUT (device-undertest) are immersed in Fluorinert<sup>TM</sup> to avoid breakdown through air.

If the drain and gate current rise at the same time and show similar values, i.e. the drain current is primarily flowing into the gate, the breakdown is limited by the device surface, AlGaN barrier or passivation depicted in Fig. 3.4(1). If the drain current rises independently from the gate current, the breakdown is buffer related and can be lateral between drain and source [see Fig. 3.4(2)] or vertical between drain and substrate [see Fig. 3.4(3)]. To differentiate the two possibilities, an additional vertical breakdown measurement is performed, in which the gate and source terminals are disconnected and the voltage between drain and subtrate  $V_{vert}$  is increased until a vertical current  $I_{vert}$  of 1 A/cm<sup>2</sup> is measured. If the shapes of  $I_D$  and  $I_{vert}$  are similar, a vertical leakage path is dominant, otherwise a lateral one. Therefore, the example curve shows a limitation by vertical breakdown.

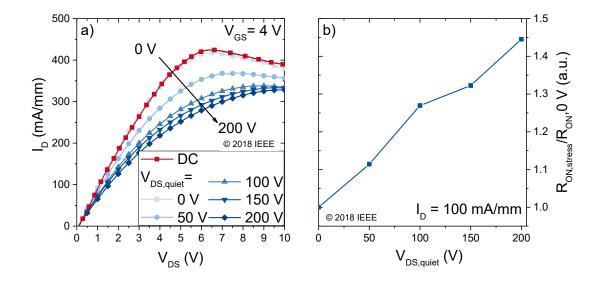

#### 3.3. Pulsed-I-V

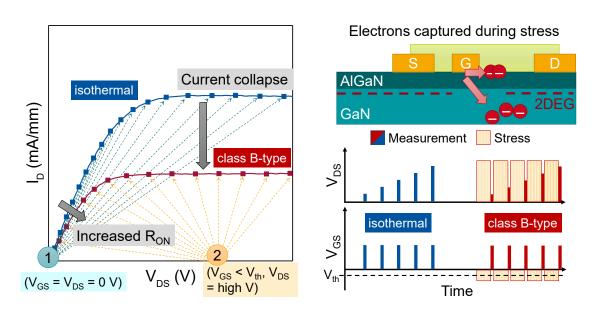

Power transistors are commonly operated in switched mode, which is accompanied by charging and discharging of electron traps within the structure. To emulate "real" device operation and investigate trap dynamics, pulsed current-voltage (pulsed-I-V) output characterization is performed [72, 73]. Here, the device is kept in a quiescent bias point for a longer period of time and then short-pulsed to the individual measurement points.

**Figure 3.4.:** Schematic cross section of an HFET with a breakdown measurement configuration and a schematic measurement result.

The duty cycle between quiescent and measurement point is usually in the scale of 0.1%. The measurement is then repeated for various quiescent points to investigate different effects. This pulsed measurement scheme is depicted in Fig. 3.5.

In an isothermal measurement, the quiescent bias point is chosen to  $V_{DS} / V_{GS} = (0, 0)$  [see Fig. 3.5(1)]. In a DC setup, the constant current flow leads to a self-heating of the device, which increases the resistance of the 2DEG. By pulsing from (0, 0) to the individual measurement points for only short periods of time, an output characteristic without any self-heating can be measured (blue curve in Fig. 3.5).

For a class B-type measurement [74], the quiescent bias point is chosen to a gatesource voltage below  $V_{th}$  to switch the device off, and a high drain-source voltage  $V_{DS}/V_{GS} = (\langle V_{th}, high value)$  [see Fig. 3.5(2)]. During this OFF-state stress, electrons can be injected from the gate edge into surface traps or the passivation and from the drain edge to buffer traps. These captured electrons deplete the 2DEG, thus a lower current is sensed during the ON-state measurement pulses (virtual gating, see section 2.6.2) and  $R_{ON}$  is increased. The difference in saturation current is called current collapse, while the ratio  $R_{ON,classB}/R_{ON,(0,0)}$  is called dynamic  $R_{ON}$  increase.

**Figure 3.5.:** Illustration of the pulse measurement scheme. The left side shows example measurement curves for the isothermal (1) and class B-type measurement (2). The right side shows the electron capture during OFF-state stress and a timing diagram of  $V_{DS}/V_{GS}$  vs. time with the alternating stress/measurement scheme.

## 4. Threshold Voltage Engineering and Stability of MISHFET

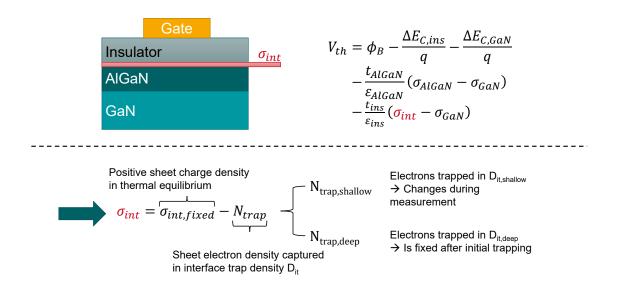

In the fundamentals chapter, it was implicitly assumed that the charge condition at the oxide/AlGaN interface is fixed (see Fig.2.10). When analyzing real devices, charging and discharging dynamics of additional interface trap states have to be considered, which change this charge condition. The resulting instabilities can make circuit design challenging or even impossible. Particularly the resulting threshold voltage shift (see Eq. (2.14)) and its transient behavior are important for the operation of normally-off MISHFET.

In the following, the common gate dielectric deposition method atomic layer deposition, is introduced. Next, the different types of interface states, their energetic distribution within the bandgap and their origin are discussed. Consequently, the impact of the gate insulator in MISHFET is shown and two different techniques to manipulate the interface properties, thermal annealing (PDA) and oxygen plasma annealing are investigated. The aim is the reduction of the fixed positive interface charge and interface trap density to achieve a stable, ideally positive,  $V_{th}$  shift  $\Delta V_{th}$  by the gate dielectric. The fundamental threshold voltage shift limitations of MISHFET devices will be discussed and the chapter is concluded by presenting a memory device, which employs the effects shown throughout this chapter.

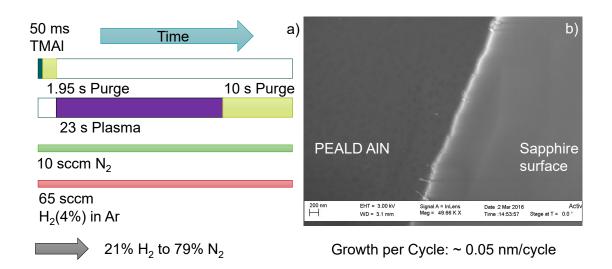

### 4.1. Plasma-Enhanced Atomic Layer Deposition

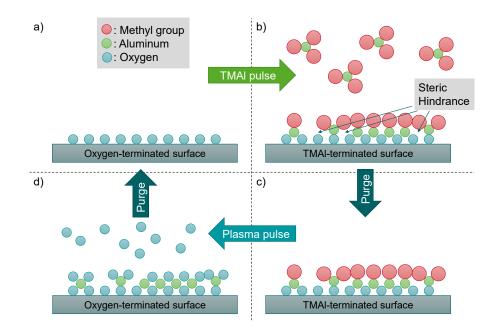

Quality and thickness control of the gate dielectric are vital for achieving the desired device properties. The method of choice for the deposition of thin dielectrics is plasmaenhanced atomic layer deposition (PEALD). The basic working principle is an alternating, self-terminating deposition of an atomic layer of metal and nonmetal. Due to this process scheme, a monolayer-thickness control [75] and very good conformity can be achieved [76].

**Figure 4.1.:** Schematic overview of a full process cycle of PEALD aluminum oxide. a) Oxygenterminated surface b) After a TMAl pulse, the TMAl reacts with the oxygen-terminated surface c) TMAl-terminated surface and purge of the remaining molecules d) Plasma-ignition of the oxygen purge gas leads to highly reactive oxygen radicals which react with the TMAl-terminated surface.

The full deposition cycle for PEALD of aluminum oxide  $(AIO_x)$  is shown in Fig. 4.1. After cleaning the sample, an oxygen-terminated surface is assumed [Fig. 4.1(a)]. A tri-methyl-aluminum (TMAI) pulse is introduced into the chamber which reacts with the oxygen-terminated surface and splits-off the methyl groups [Fig. 4.1(b)]. After the whole surface is saturated with TMAI, the process automatically terminates and the remaining TMAI is purged from the chamber [Fig. 4.1(c)]. Next, the oxygen purge gas is plasma-ignited in a remote chamber. This creates highly reactive oxygen radicals, which react with the aluminum-terminated surface and form a (new) layer of AlO<sub>x</sub>. Ideally, each full cycle deposits a monolayer of AlO<sub>x</sub>, but due to incomplete reactions and steric hindrance, the deposition is less than a monolayer [75]. The deposited AlO<sub>x</sub> thin films are amorphous, but thin films of other materials can also be crystalline [77].

In this work, the following pulse scheme was used: 30 ms TMAl, 1970 ms purge, 3000 ms plasma, 1000 ms purge. The chamber pressure was 20 Pa and the deposition temperature was 250 °C. The resulting deposition rate was 0.105 nm per cycle and the relative dielectric constant of the resulting thin film was  $\varepsilon_r = 8$ , which is comparable to literature values [78].

**Figure 4.2.:** Band diagram of the different types of traps within the bandgap. Furthermore, the capture and emission processes are depicted.

#### 4.2. Interface Trap States

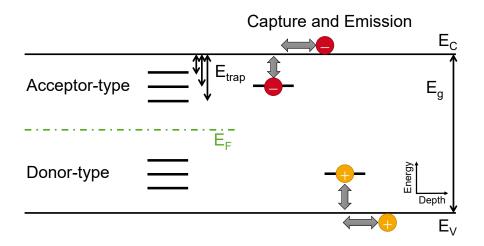

The interface charge density  $\sigma_{int}$  was considered as fixed charge in the previous chapter. But due to impurity incorporation during deposition, dangling bonds and defects, dielectrics and dielectric/semiconductor interfaces commonly show bulk/interface states, respectively. These so-called trap states capture and emit electrons and have a high impact on the device properties, as they change the charge condition within the structure, effectively changing  $\sigma_{int}$ . They are classified into two types, namely acceptor- and donor-type traps in analogy to dopants.

Fig. 4.2 shows a schematic of these two trap types in the semiconductor bandgap. In thermal equilibrium, the trap states are occupied in their relation to the Fermi level. In the presence of free charge carriers, acceptor-type traps are able to capture electrons and become negatively charged, while donor-type traps capture holes becomes positively charged. As no free states in a more energetically-favorable position exist, the charge carriers are now trapped.

The transient behavior of trap states is related to their energetic depth within the bandgap  $E_{trap}$ . It can be either related to the distance between the trap state and the conduction band edge or valence band edge for acceptor-type traps and donor-type traps, respectively. While the capture process is commonly considered to be very fast, the mean time until an emission process occurs  $\tau$  (emission time constant) can be described by Shockley-Read-Hall statistics [79]:

$$\tau = \frac{1}{\nu_{\rm th} \sigma_{\rm th} N_{\rm c}} \exp\left(\frac{E_{\rm trap}}{k_{\rm B} T}\right) \tag{4.1}$$

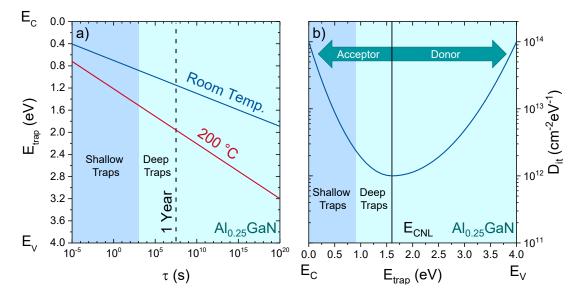

**Figure 4.3.:** Trap emission time constants and distribution of trap density vs. their distance from the AlGaN conduction band edge  $E_{trap}$ . Traps are classified in deep and shallow traps whether they emit captured electrons during the measurement time frame. a)  $E_{trap}$  vs. trap emission time constant. b) Trap density  $D_{it}$  vs.  $E_{trap}$ . Traps from the charge-neutrality level  $E_{CNL}$  towards conduction band edge are acceptor-type, while they are donor-type towards the valence band edge. Images after [79].

where  $v_{th}$  is the thermal velocity of the electrons,  $\sigma_{th}$  the trap cross section,  $N_c$  the free state density in the conduction/valence band,  $k_B$  the Boltzmann constant and T the absolute temperature in Kelvin.

Fig. 4.3(a) shows  $E_{trap}$  related to the conduction band edge of AlGaN with 25% Al vs.  $\tau$ . Traps that are located deeper in the bandgap have a significantly longer  $\tau$  than traps near the band edge [see Eq. (4.1)]. At room temperature, traps with  $E_{trap} = 1.15 \text{ eV}$  already have  $\tau$  of approx. one year. Increasing the temperature reduces  $\tau$  strongly, which is the foundation of various trap characterization techniques [80].

Based on their emission time constant  $\tau$ , traps are additionally classified into shallow and deep traps. Shallow traps have  $\tau$  in the range of the measurement duration used to characterize the traps, therefore the impact of a change of the charge state can be observed. Deep traps have  $\tau$  longer than the measurement time and thus act as fixed charge. The focus in this work is on traps that are located at the interface between insulator and semiconductor, and capture/emit electrons.

Fig. 4.3(b) shows the energetic distribution of the interface trap density in the bandgap  $D_{it}$  vs.  $E_{trap}$ . The U-shape distribution is based on the unified disorder-induced gap state model by Hasegawa and Ohno [81] and was experimentally confirmed for oxide/III-nitride interfaces by Matys et al. [82]. According to this model, the interface states

**Figure 4.4.:** Overview of the different parts of the interface charge density  $\sigma_{int}$ , which is influencing V<sub>th</sub>. The equation in the top right corner is Eq. (2.14).

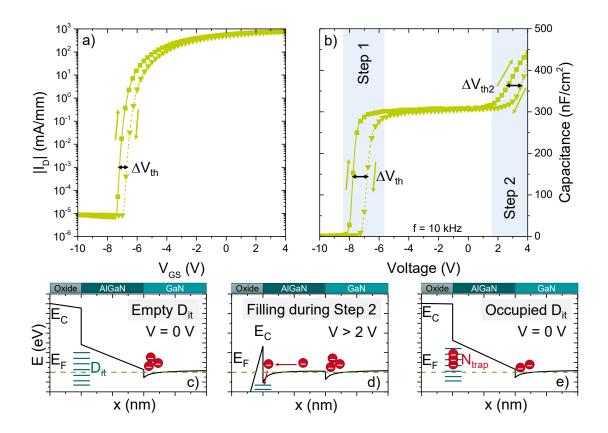

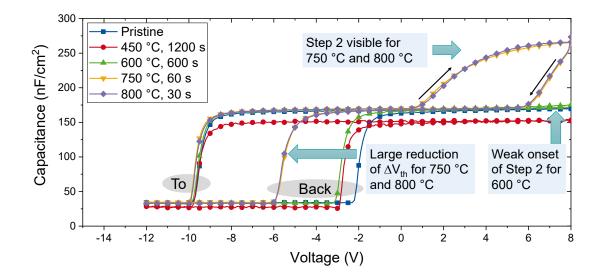

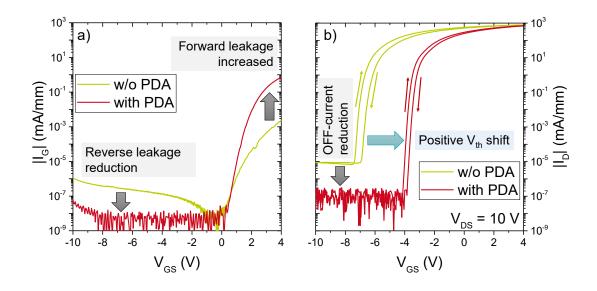

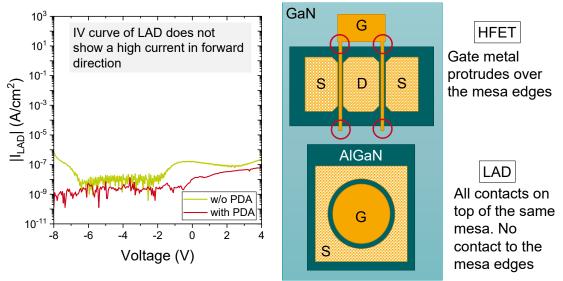

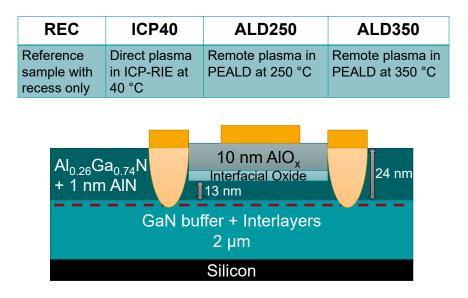

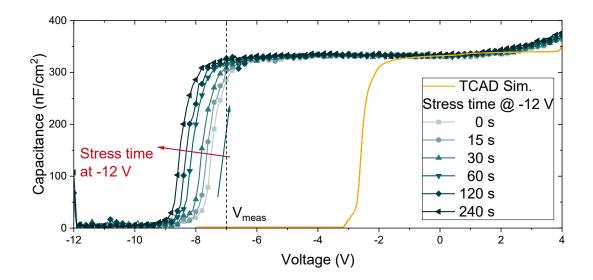

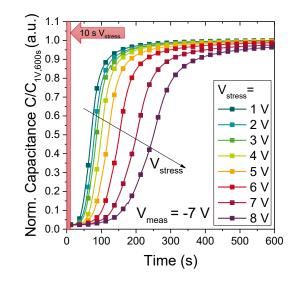

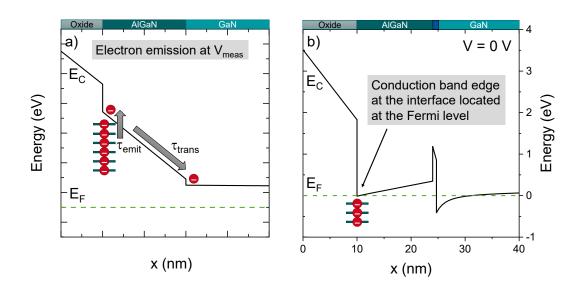

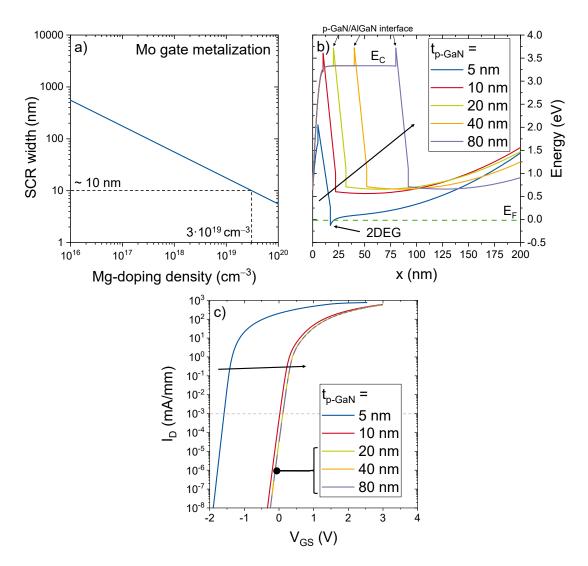

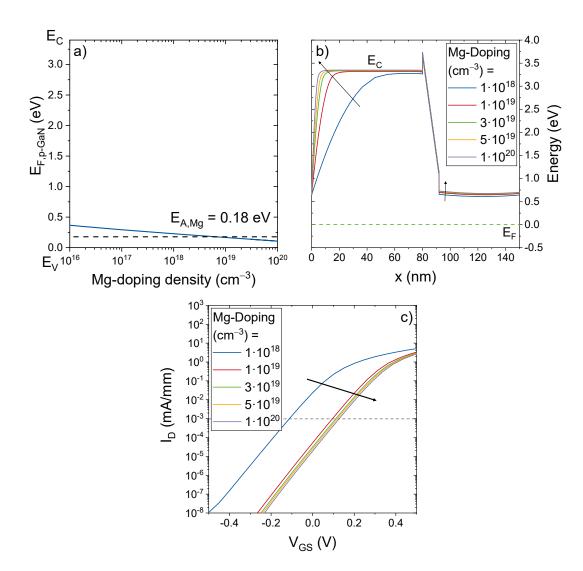

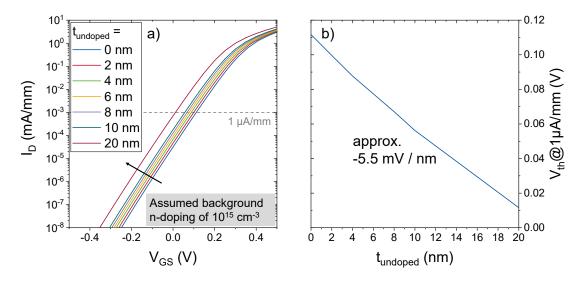

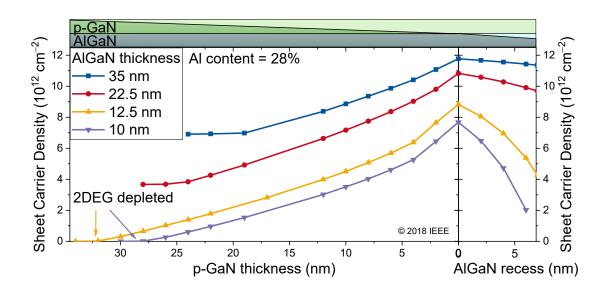

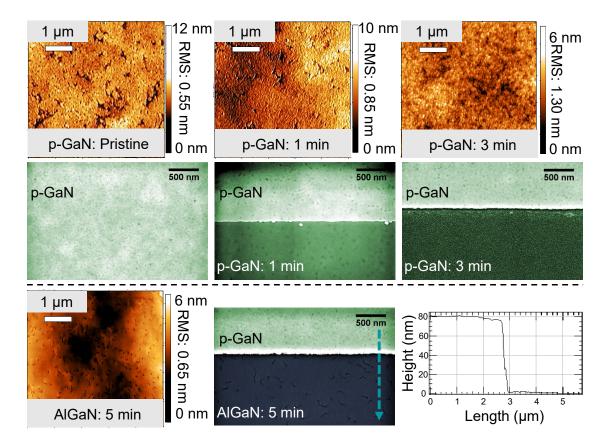

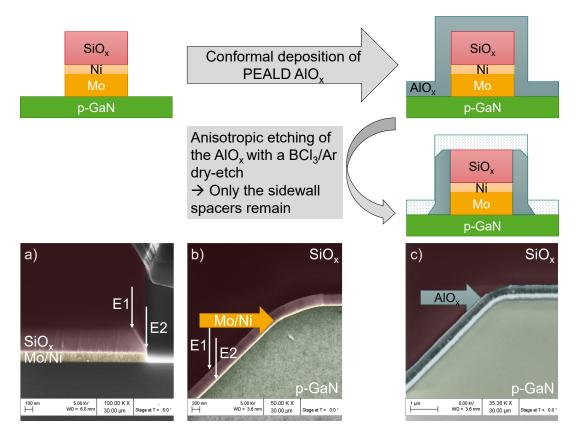

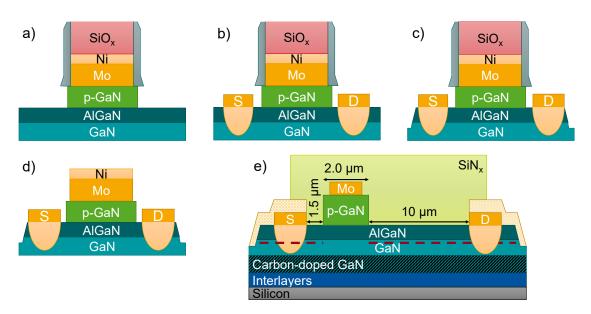

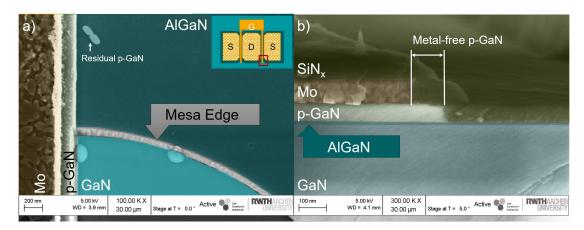

originate from dangling bonds caused by crystal disorder of the semiconductor surface. The U-shape is caused by the nature of the bonding states to minimize their energy during formation and can be described by an exponential decay of  $D_{it}$  towards the charge-neutrality level  $E_{CNL}$  [82]. The charge-neutrality level  $E_{CNL}$  is defined as the Fermi level position, for which the interface is charge neutral, and is only used in this work for the explanation of this model. The model states further, that trap states from  $E_{CNL}$  towards the conduction band are acceptor-type and donor-type towards the valence band. Higher levels of disorder at the insulator/AlGaN interface lead to a higher  $D_{it}$ , which decreases the device stability. A more detailed explanation of the capture and emission processes of  $D_{it}$  during device operation and the influence on  $V_{th}$  is given in the next section.  $D_{it}$  will be used for the interface trap density and the interface traps synonymously for the sake of simplicity.